آموزش طراحی سیستم با استفاده از Verilog - آخرین آپدیت

System Design using Verilog

پس از اتمام این دوره، فراگیران قادر خواهند بود:

(1) مفاهیم معیارهای طراحی را که باید توسط یک مهندس طراح بهینه شود را درک کنید

(2) مفاهیم فناوری طراحی آی سی را درک کنید

(3) اجرای منطق را با استفاده از فناوری آی سی عملکرد ثابت، فناوری ASIC سفارشی کامل، و فناوری ASIC نیمه سفارشی درک کنید

(4) مزایا و معایب اجرای منطق را با استفاده از فناوری آی سی عملکرد ثابت، فناوری ASIC سفارشی کامل، و فناوری ASIC نیمه سفارشی درک کنید

(5) مفهوم پیاده سازی منطق در PLD ها را درک کنید

(6) مفهوم پیاده سازی منطق در FPGA را درک کنید

(7) جریان طراحی آی سی را درک کنید

(8) نقش HDL را در طراحی سیستم درک کنید

(9) مفاهیم ساختارهای مختلف زبان Verilog را درک کنید

(10) اپراتورهای مختلف و کاربرد آنها در کدنویسی Verilog را درک کنید

(11) نحوه استفاده از نرم افزار Xilinx برای نوشتن کد Verilog را بدانید

(12) نحوه استفاده از نرم افزار Xilinx برای شبیه سازی کد Verilog را بدانید

(13) نحوه استفاده از نرم افزار Xilinx برای پیاده سازی کد Verilog را بدانید

(14) منطق ترکیبی را با استفاده از سبک مدلسازی رفتاری اجرا کنید

(15) منطق ترکیبی را با استفاده از سبک مدلسازی جریان داده

پیادهسازی کنید(16) منطق ترکیبی را با استفاده از سبک مدلسازی ساختاری اجرا کنید

(17) منطق ترتیبی را با استفاده از سبک مدلسازی رفتاری اجرا کنید

(18) با استفاده از سبک مدلسازی جریان داده، منطق ترتیبی را اجرا کنید

(19) منطق ترتیبی را با استفاده از سبک مدلسازی ساختاری اجرا کنید

(20) منطق را با استفاده از ترانزیستورهای Mos

پیاده سازی کنیدفناوری طراحی آی سی IC Design Technology

-

معیارهای طراحی Design Metrics

-

فناوری آی سی کارکرد ثابت Fixed Function IC Technology

-

فناوری ASIC سفارشی کامل Full Custom ASIC Technology

-

فناوری ASIC نیمه سفارشی Semi-Custom ASIC Technology

-

نقش HDL در طراحی سیستم HDL Role in System Design

-

فناوری PLD (PLA) PLD Technology (PLA)

-

فناوری PLD (PAL) PLD Technology (PAL)

-

FPGA (معماری) FPGA (Architecture)

-

FPGA (نمونههای پیادهسازی منطق) FPGA (Logic Implementation Examples)

-

خود را به چالش بکشید - 1 Challenge Your Self - 1

مقدمه ای بر نرم افزار Verilog و Xilinx Introduction to Verilog and Xilinx Software

-

مقدمه ای بر Verilog Introduction to Verilog

-

سطح انتزاع Level of Abstraction

-

آشنایی با نرم افزار Xilinx Introduction to Xilinx Software

-

انواع داده ها (انواع شبکه) Data Types (Net Types)

-

انواع داده ها (انواع ثبت نام) Data Types (Register Types)

-

اپراتور (اپراتور Bitwise) Operator (Bitwise operators)

-

اپراتور (منطقی و کاهش) Operator (Logical & Reduction)

-

عملگر (حسابی، رابطه ای و شیفت) Operator (Arithmetic, Relational & Shift)

-

اپراتور (الحاق، شرطی و تکرار) Operator (Concatenation, Conditional & Replication)

-

خود را به چالش بکشید - 2 Challenge Your Self – 2

مقدمه ای بر سطوح مختلف مدل سازی Introduction to different level of modeling

-

مقدمه ای بر مدل سازی سطح ساختار Introduction to Structure Level Modeling

-

مقدمه ای بر مدل سازی سطح رفتاری Introduction to Behavioural Level Modeling

-

مقدمه ای بر مدل سازی سطح جریان داده Introduction to Dataflow Level Modeling

نیمکت آزمون Testbench

-

نیمکت تست - (قسمت اول) Test Bench-(Part I)

-

نیمکت تست - (قسمت دوم) Test Bench -(Part II)

-

نیمکت تست - (قسمت سوم) Test Bench-(Part III)

مدلسازی ساختار Structure Modeling

-

مدلسازی ساختار (2 تا 1 مولتی پلکسر) Structure Modeling (2 to 1 Multiplexer)

-

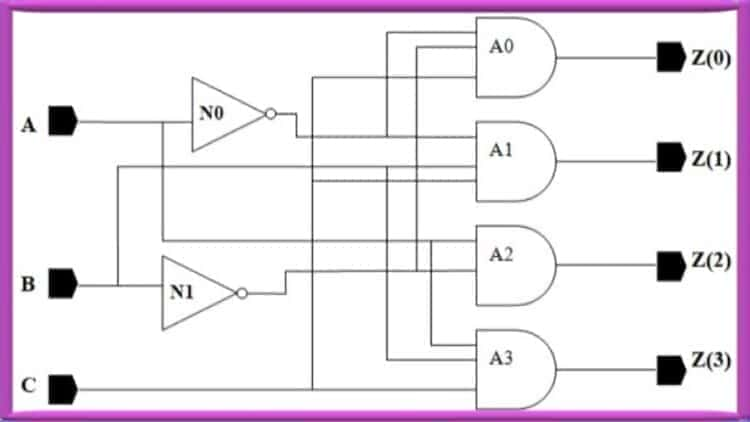

مدلسازی ساختار (2 تا 4 رمزگشا) Structure Modeling (2 to 4 Decoder)

-

مدلسازی ساختار (جمع کننده 3 بیتی) قسمت - اول Structure Modeling (3-Bit Adder) Part - I

-

مدلسازی ساختار (جمع کننده 3 بیتی) قسمت - دوم Structure Modeling (3-Bit Adder) Part - II

مدل سازی رفتاری Behavioural Modeling

-

اظهارات رویه ای Procedural Statements

-

بیانیه های متوالی (اگر-دیگر) قسمت اول Sequential Statements (if-else) Part-I

-

بیانیه های متوالی (اگر-دیگر) قسمت دوم Sequential Statements (if-else) Part-II

-

بیانیه های متوالی (اگر-دیگر) قسمت سوم Sequential Statements (if-else) Part-III

-

رمزگشای 2 تا 4 با استفاده از بیانیه if-else 2 to 4 Decoder using if-else Statement

-

مقایسه کننده با استفاده از بیانیه «اگر-دیگر». Comparator using “if-else” Statement

-

نمایش نرم افزار Comparator Software demonstration of Comparator

-

مولتی پلکسر 2 به 1 با استفاده از عبارت "case". 2 to 1 Multiplexer using “case” Statement

-

مولتی پلکسر 4 به 1 با استفاده از عبارت "case". 4 to 1 Multiplexer using “case” Statement

-

2 تا 4 رمزگشا با استفاده از عبارت "case". 2 to 4 Decoder using “case” Statement

-

مقایسه کننده 1 بیتی با استفاده از بیانیه "مورد". 1 Bit Comparator using “case” Statement

-

رمزگشای BCD به 7 بخش با استفاده از بیانیه "مورد". BCD to 7 Segment Decoder using “case” Statement

-

عبارات متوالی - (حلقه) Sequential Statements - (loop)

مدل رفتار - مدارهای متوالی Behaviourl Model - Sequential Circuits

-

کد Verilog D Flip Flop Verilog code of D Flip Flop

-

کد Verilog JK Flip Flop Verilog code of JK Flip Flop

-

کد Verilog T Flip Flop Verilog code of T Flip Flop

-

کد Verilog 3 بیت شمارنده Verilog code of 3 Bit Counter

-

موازی در موازی خارج ثبت نام Parallel In Parallel Out Register

-

سریال به صورت موازی از ثبت نام Serial In Parallel Out Register

-

سریال در سریال خارج ثبت نام Serial In Serial Out Register

چندگانه همیشه مسدود شود Multiple Always Block

-

چندین بلوک همیشه - (مثال) Multiple always block - (Example)

-

چندین بلوک همیشه - (D Flip Flop) Multiple always block – (D Flip Flop)

-

چندین بلوک همیشه - (2 تا 4 رمزگشا) Multiple always block - (2 to 4 Decoder)

بیانیه های مسدود و غیر انسداد Blocking and Non-blocking Statements

-

بیانیه مسدود کردن Blocking Statement

-

بیانیه عدم انسداد Non-Blocking Statement

چند نمونه از مدارهای ترکیبی Few Examples of Combinational Circuits

-

مدل Verilog از تفریق کننده کامل Verilog Model of Full Subtractor

-

مبدل باینری به خاکستری Binary to Gray Converter

-

مبدل خاکستری به باینری Gray to Binary Converter

-

کد Verilog از 1 تا 2 Demultiplexer Verilog Code of 1 to 2 Demultiplexer

-

رمزگذار اولویت Priority Encoder

مدل سازی سطح سوئیچ Switch Level Modeling

-

سوئیچ "cmos" (قسمت اول) “cmos” Switch (Part I)

-

سوئیچ "cmos" (قسمت دوم) “cmos” Switch (Part II)

-

سوئیچ "cmos" (قسمت سوم) “cmos” Switch (Part III)

-

سوئیچ "cmos" (قسمت چهارم) “cmos” Switch (Part IV)

https://donyad.com/d/809b9b

Dr Yogesh Misra

Dr Yogesh Misra

استاد موسسه فناوری GMR هند

نمایش نظرات