آموزش طراحی فیزیکی (PD)، سنتز و تحلیل استاتیک زمان (STA) با جریان کاری ابزارهای Cadence و Synopsys - آخرین آپدیت

دانلود Synthesis-STA-Physical Design(PD):Cadence+Synopsys Tool flow

آموزش جامع طراحی ASIC: سنتز، تحلیل زمانبندی ایستا (STA) و طراحی فیزیکی

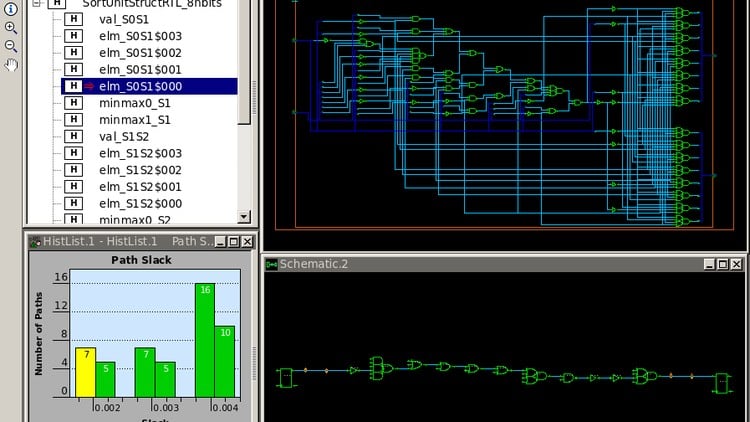

یادگیری کامل جریان طراحی ASIC با استفاده از ابزارهای Cadence Genus, Tempus, Innovus و Synopsys ICC2.

مروری بر سرفصلهای دوره

- مقدمهای بر جریان طراحی ASIC

- سنتز منطقی در مقابل سنتز فیزیکی

- مفاهیم و تعاریف زمانبندی

- تحلیل زمانبندی ایستا (STA)

- مسیرهای زمانبندی، محدودیتها و مُدها

- اجرای مثال سنتز با ابزار Cadence Genus

- اجرای مثال STA با ابزار Cadence Tempus

- جریان طراحی فیزیکی با استفاده از ابزار Cadence Innovus

- طرحریزی (Floorplan)

- چیدمان (Placement)

- سنتز درخت ساعت (CTS)

- مسیریابی (Routing)

پیش نیازها

- مبانی طراحی RTL با استفاده از Verilog

- مبانی دیجیتال

- زبان Verilog

بخش 1: سنتز و تحلیل زمانبندی ایستا (STA)

این دوره برای تمام سطوح دانشجویان و مهندسان علاقهمند به کسب دانش در زمینه سنتز ASIC و STA مناسب است. ایده آل برای دانشجویان الکترونیک، کارآموزان و مهندسانی که قصد شروع کار در حوزه VLSI را دارند.

- 1. مروری بر جریان ASIC

- 2. سنتز منطقی - ورودیها و خروجیهای سنتز، محدودیتهای سنتز، کتابخانهها

- 3. سنتز منطقی II - دموی سنتز با استفاده از ابزار Cadence Genus

- 4. سنتز فیزیکی - فرمتهای مختلف فایل و توضیحات، ابعاد فیزیکی گیتها

- 5. مفاهیم زمانبندی - زمان Setup، زمان Hold، Slack، تخلفات، بودجه زمانبندی

- 6. تحلیل زمانبندی ایستا (STA)

- 7. مسیرهای زمانبندی - Clock to output، تاخیر انتشار، تاخیر ورودی، تاخیر خروجی، STA با استفاده از ابزار Cadence Tempus

- 8. محدودیتهای زمانبندی و مُدهای مختلف - MMMC

- 9. استثنائات زمانبندی - False path، Multi cycle path

- 10. تمرین سنتز و STA - APB Timer

بخش 2: جریان طراحی فیزیکی با استفاده از ابزارهای Cadence - طراحی APB UART

- 11. ورودیهای طراحی فیزیکی

- 12. مراحل ابزار Innovus

- 13. طرحریزی (Floorplan)

- 14. دموی طرحریزی

- 15. چیدمان (Placement)

- 16. سنتز درخت ساعت (CTS)

- 17. دموی CTS

- 18. مسیریابی (Routing)

- 19. SDC_MMMC_PVT Corners

- 20. تایید فیزیکی

- 21. تمرین طراحی فیزیکی با استفاده از جریان Cadence Innovus - طراحی APB Timer

بخش 3: جریان طراحی فیزیکی با استفاده از ابزارهای Synopsys - طراحی پردازنده RISCV

- 22. DC Synthesis

- 23. معرفی جریان ICC2

- 24. مقداردهی اولیه ICC2

- 25. طرحریزی ICC2

- 26. PowerPlan ICC2

- 27. چیدمان ICC2

- 28. CTS ICC2

- 29. مسیریابی و تکمیل چیپ ICC2

- 30. Formality - بررسی معادل منطقی (LEC)

- 31. PrimeTime - STA پس از چیدمان

- 32. تمرین سنتز و طراحی فیزیکی با استفاده از ابزارهای Synopsys

این دوره برای تمام سطوح دانشجویان و مهندسان علاقهمند به کسب دانش در زمینه سنتز ASIC و STA مناسب است. ایده آل برای دانشجویان الکترونیک، کارآموزان و مهندسانی که قصد شروع کار در حوزه VLSI را دارند.

تمام موضوعات با مثالهای دقیق، همراه با نمودارها در صورت نیاز، توضیح داده شدهاند.

توضیحات واضح؛ تکالیف در انتهای دوره برای تمرین مثالهای عملی اضافه شدهاند.

این آموزش توسط متخصصان با تجربه از صنعت VLSI ارائه میشود که روی پروژههای متعددی کار کردهاند و چیپ طراحی کردهاند.

برای بهترین نتیجه از این دوره، لطفاً با استفاده از ابزارها به صورت عملی کار کنید (ممکن است در موسسات/شرکتهای شما در دسترس باشد).

با آرزوی موفقیت - یادگیری خوبی داشته باشید!

سنتز و تحلیل زمانبندی استاتیک (STA) Synthesis and Static Timing Analysis(STA)

-

فرایند ASIC ASIC Flow

-

سنتز منطقی – قسمت اول Logical Synthesis - Part I

-

سنتز منطقی – قسمت دوم Logical Synthesis - Part II

-

سنتز فیزیکی Physical Synthesis

-

مفاهیم زمانبندی Timing Concepts

-

تحلیل زمانبندی استاتیک (STA) Static Timing Analysis (STA)

-

مسیرهای زمانبندی و STA با استفاده از ابزار Tempus Timing Paths and STA using Tempus tool

-

محدودیت ها و حالت های زمانبندی Timing Constraints and Modes

-

استثنائات زمانبندی Timing Exceptions

-

تکلیف سنتز و STA - طراحی تایمر APB Synthesis and STA assignment - APB Timer design

طراحی فیزیکی با استفاده از جریان Cadence Innovus - پروژه طراحی APB UART Physical Design using Cadence Innovus Flow - APB UART Design Project

-

ورودی ها به طراحی فیزیکی Inputs to Physical Design

-

مراحل ابزار Innovus Innovus tool Steps

-

برنامه ریزی جانمایی (Floorplan) Floorplan

-

دموی برنامه ریزی جانمایی (Floorplan) Floorplan Demo

-

جانمایی (Placement) Placement

-

سنتز درخت ساعت (CTS) Clock Tree Synthesis(CTS)

-

دموی سنتز درخت ساعت (CTS) Clock Tree Synthesis(CTS) Demo

-

مسیرکشی (Routing) Routing

-

گوشه های SDC_MMMC_PVT SDC_MMMC_PVT Corners

-

تایید فیزیکی Physical Verification

-

تکلیف طراحی فیزیکی – طراحی تایمر Physical Design Assignment - Timer Design

سنتز، طراحی فیزیکی، STA با استفاده از ابزار Synopsys - پروژه پردازنده RISCV Synthesis, Physical Design, STA using Synopsys Tool - RISCV Processor Project

-

سنتز RTL با استفاده از DC Compiler RTL Synthesis using DC Compiler

-

معرفی - جریان ICC2 Introduction - ICC2 Flow

-

ICC2 - مقداردهی اولیه ICC2 - Initialization

-

برنامه ریزی جانمایی (Floorplan) با استفاده از ICC2 Floorplan using ICC2

-

برنامه ریزی توان (Powerplan) با استفاده از ICC2 Powerplan using ICC2

-

جانمایی (Placement) با استفاده از ICC2 Placement using ICC2

-

سنتز درخت ساعت (CTS) با استفاده از ICC2 Clock Tree Synthesis (CTS) using ICC2

-

مسیرکشی و تکمیل چیپ با استفاده از ICC2 Routing and Chip Finishing using ICC2

-

بررسی هم ارزی منطقی (LEC) با استفاده از Formality Logic Equivalence Check(LEC) using Formality

-

STA پس از جانمایی (Post Layout STA) با استفاده از PrimeTime Post Layout STA using PrimeTime

-

تکلیف سنتز، طراحی فیزیکی و STA برای جریان ابزار Synopsys Synthesis, Physical Design and STA assignment for Synopsys Tool flow

https://donyad.com/d/5b7e79

VLSI Mentor

VLSI Mentor

متخصص VLSI، مدیرعامل، فناوریهای VLSI اکسل

![Kotlin کاربردی برای توسعه برنامه اندروید [ویدئو] Kotlin کاربردی برای توسعه برنامه اندروید [ویدئو]](https://donyad.com/course/getimg/68a71bed-96b7-4162-a797-484a1f438250.jpg)

![عملی با ویندوز سرور 2019 [ویدئو] عملی با ویندوز سرور 2019 [ویدئو]](https://donyad.com/course/getimg/d0afbc10-f018-40d4-ba7c-2fd7fe48f447.jpg)

نمایش نظرات