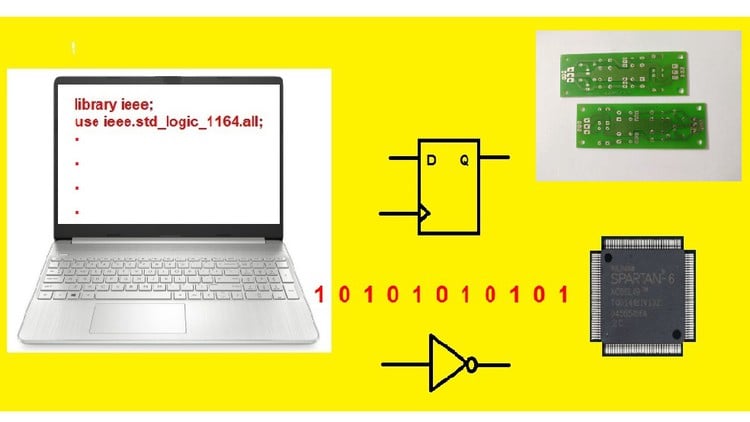

آموزش گام به گام برنامه نویسی VHDL برای زایلینکس FPGA و CPLD - آخرین آپدیت

دانلود Step By Step VHDL Programming for Xilinx FPGA & CPLD

آموزش جامع برنامهنویسی VHDL برای FPGA زایلینکس و طراحی PCB

مهارتهای ضروری برای دانشجویان مهندسی الکترونیک:

برنامهنویسی VHDL | سنتز و شبیهسازی | قطعات FPGA و CPLD زایلینکس | مجموعه طراحی Xilinx ISE و پیادهسازی

پیشنیازهای دوره:

- مفاهیم طراحی منطق دیجیتال (Digital Logic Design Concepts)

- دانش پایه از هر زبان برنامهنویسی (مانند برنامهنویسی C)

دانشجوی عزیز، خوش آمدید!

این دوره مقدماتی با محتوای سطح پایه بر برنامهنویسی VHDL به عنوان یک مرجع برای مبتدیان تمرکز دارد و برای دانشجویان پلیتکنیک الکترونیک، مهندسی، دانشگاهی و همچنین علاقهمندان به الکترونیک طراحی شده است.

علاوه بر محتوای برنامهنویسی VHDL با استفاده از نرمافزار Xilinx ISE Webpack، مباحث طراحی PCB در سطح بسیار ابتدایی (فقط طراحی PCB تک لایه) با استفاده از نرمافزار EasyEDA نیز به این دوره اضافه شده است.

اگر دانشجوی الکترونیک هستید، میتوانید محتوای طراحی PCB را به عنوان یک بخش مکمل و ارزشمند در نظر بگیرید.

در صورتی که فقط به برنامهنویسی VHDL علاقهمند هستید، میتوانید از بخش طراحی PCB صرفنظر کنید.

تمام محتوای این دوره بر اساس نرمافزارهای رایگان و قابل دانلود به صورت آنلاین یا متنباز (Opensource) برای طراحی و برنامهنویسی است.

1. برنامهنویسی VHDL با استفاده از Xilinx ISE Webpack

نرمافزار Xilinx ISE Webpack یک ابزار رایگان و قابل دانلود (پس از ایجاد حساب کاربری در وبسایت Xilinx) است. مثالهای برنامهنویسی VHDL برای مدارهای منطقی ترکیبی و ترتیبی (Combinational & Sequential Digital Logic) با رویکرد گام به گام (شامل برنامه VHDL، تست بنچ VHDL، سنتز و شبیهسازی رفتاری) توضیح داده شدهاند. همچنین مثالهای برنامهنویسی بر اساس ماشینهای حالت متناهی (FSMs) مبتنی بر VHDL تشریح شدهاند.

2. مبانی طراحی PCB (فقط مثالهای طراحی PCB تکلایه) با نرمافزار EasyEDA

در این بخش، مثالهای طراحی PCB تکلایه با استفاده از نرمافزار آنلاین و رایگان EasyEDA (پس از ایجاد حساب کاربری در وبسایت EasyEDA) توضیح داده شدهاند. مباحث شامل طراحی شماتیک، طراحی لایهبندی PCB (جانمایی قطعات) و مسیردهی ترکها (Track Routing) با رویکرد تکلایه است. همچنین مثالهای طراحی PCB بر اساس قطعات Through-Hole (پایهدار) و قطعات SMT (Surface Mount Technology - نصب سطحی) ارائه شدهاند.

در ابتدا، عنوان دوره "برنامهنویسی گام به گام VHDL برای CPLD و FPGA زایلینکس" بود که یک دوره VHDL برای سطح مبتدی به شمار میرفت.

رویکرد من بر افزودن و بهروزرسانی مستمر محتوای این دوره است تا به طور خاص برای دانشجویان پلیتکنیک الکترونیک، مهندسی، دانشگاهی و همچنین علاقهمندان به حوزه الکترونیک و FPGA مفید باشد.

تاریخچه بهروزرسانی دوره:

- بهروزرسانی دوم (فوریه 2021): اضافه شدن مبانی طراحی PCB (طراحی PCB تکلایه) با استفاده از نرمافزار EasyEDA.

- بهروزرسانی اول (اکتبر 2021): اضافه شدن مثالهای ماشینهای حالت متناهی (FSM) با برنامهنویسی VHDL.

- انتشار اولیه دوره (سپتامبر 2020): محتوای برنامهنویسی VHDL با استفاده از نرمافزار Xilinx ISE Webpack.

درباره مدرس دوره:

مدرس این دوره دارای بیش از 22 سال تجربه طراحی و آموزش پس از اخذ مدرک M.Tech (کارشناسی ارشد فناوری) در رشته طراحی و فناوری الکترونیک است. این تجربیات گسترده شامل حوزههای زیر میشود:

- طراحی مدارهای الکترونیکی (Electronic Circuit Design)

- سیستمهای نهفته (Embedded System)

- طراحی VLSI: برنامهنویسی VHDL و Verilog برای FPGA و CPLDهای Xilinx با استفاده از ابزارهای Xilinx ISE و Xilinx Vivado.

- برنامهنویسی PSOC1 با Cypress PSOC Designer و PSOC3/PSOC4 با Cypress PSOC Creator.

- برنامهنویسی میکروکنترلرها:

- STM32 (مبتنی بر هسته ARM 32 بیتی) با STM32cubeIDE

- خانواده MCS-51 (8051) با Keil uVision 4

- ATMega 16/32/128 با Atmel AVR Studio

- Microchip PIC 16/18 با MPLAB

- برنامهنویسی آردوینو (Arduino Uno)

- MSP430 از Texas Instruments با Energia

- Raspberry Pi و Raspbian Linux

- برنامهنویسی پایتون (Python) با Python 3.9 (IDLE)، Python Thonny، Python Pycharm، Anaconda Navigator (Jupyter Notebook، Spyder Python)، Google Colab.

- برنامهنویسی PLC با Crouzet Millenium 3.

- طراحی PCB (مدار چاپی) با استفاده از نرمافزارهایی نظیر EasyEDA، Eagle (Fusion 360)، KiCad 5.1، Fritzing و Express PCB.

About IC Technology

-

فناوری IC – مقدمهای بر ASIC، FPGA و ابزارهای EDA IC Technology - Introduction to ASIC , FPGA & EDA Tools

معماری FPGA FPGA Architecture

-

معماری Xilinx FPGA SPARTAN 6 Xilinx FPGA SPARTAN 6 Architecture

مبانی زبان VHDL VHDL Language Basics

-

مبانی VHDL VHDL Basics

VHDL(CPLD) – ورود به طراحی، سنتز و اعتبارسنجی – منطق دیجیتال پایه VHDL(CPLD)-Design Entry,Synthesis & Verification - Basic Digital Logic

-

VHDL – منطق دیجیتال پایه (قسمت 1) VHDL - Basic Digital Logic ( Part 1 )

-

سنتز و شبیه سازی (ارائه) Synthesis & Simulation ( Presentation )

-

سنتز و شبیه سازی رفتاری – منطق دیجیتال پایه (قسمت 1) Synthesis & Behavioral Simulation - Basic Digital Logic ( Part 1 )

-

VHDL – منطق دیجیتال پایه (قسمت 2) VHDL - Basic Digital Logic ( Part 2 )

-

سنتز و شبیه سازی رفتاری – منطق دیجیتال پایه (قسمت 2) Synthesis & Behavioral Simulation - Basic Digital Logic ( Part 2 )

-

VHDL – منطق دیجیتال پایه (قسمت 3) VHDL - Basic Digital Logic ( Part 3 )

-

سنتز و شبیه سازی رفتاری – منطق دیجیتال پایه (قسمت 3) Synthesis & Behavioral Simulation - Basic Digital Logic ( Part 3 )

-

VHDL – منطق دیجیتال پایه (قسمت 4) VHDL - Basic Digital Logic ( Part 4 )

-

سنتز و شبیه سازی رفتاری – منطق دیجیتال پایه (قسمت 4) Synthesis & Behavioral Simulation - Basic Digital Logic ( Part 4 )

اعمال محدودیت ها بر طراحی CPLD Applying Constraints to CPLD Design

-

اعمال محدودیت ها بر طراحی VHDL (قفل کردن پین) Applying Constraints to VHDL Design ( Pin Locking )

پیاده سازی طراحی – CPLD (Xilinx) Design Implementation - CPLD ( Xilinx )

-

گزارش Fitter برای CPLD Fitter Report for CPLD

یادگیری سریع: کل بخش 4 (تمام منطق ها) Fast Track Learning: Entire Section 4 (All Logics)

-

یادگیری سریع: VHDL (تمام منطق ها - بخش 4) Fast Track : VHDL ( All Logics - Section 4 )

-

یادگیری سریع: سنتز (بخش 4 - تمام منطق ها) Fast Track : Synthesis ( Section 4 - All Logics )

-

یادگیری سریع: شبیه سازی رفتاری (تمام منطق ها - بخش 4) Fast Track : Behavioral Simulation ( All Logics - Section 4 )

طراحی VHDL، تست بنچ، سنتز و اعتبارسنجی – منطق دیجیتال پایه (FPGA) VHDL Design ,Test Bench ,Synthesis & Verification - Basic Digital Logic ( FPGA )

-

VHDL – دستور Case (ارائه) VHDL - Case Statement ( Presentation )

-

کد VHDL – MUX (مالتی پلکسر 2:1) VHDL Code - MUX ( 2:1 Multiplexer )

-

فرآیند سنتز Synthesis Process

-

تست بنچ VHDL VHDL Test Bench

-

شبیه سازی رفتاری با استفاده از شبیه ساز Xilinx ISim Behavioral Simulation using Xilinx ISim Simulator

اعمال محدودیت ها بر طراحی FPGA Applying Constraints to FPGA Design

-

ویرایش محدودیت ها – قفل کردن پین Constraints Editing - Pin Locking

(FPGA) طراحی VHDL، تست بنچ، سنتز و اعتبارسنجی – منطق ترکیبی (FPGA) VHDL Design ,TestBench,Synthesis & Verification - Combinational Logics

-

کد VHDL – MUX (مالتی پلکسر 4:1) VHDL Code - MUX ( 4:1 Multiplexer )

-

تست بنچ VHDL – MUX 4:1 VHDL Test Bench - 4:1 MUX

-

سنتز: MUX 4:1 Synthesis : 4:1 MUX

-

شبیه سازی رفتاری: MUX 4:1 Behavioral Simulation : 4 : 1 MUX

-

VHDL – دیکودر VHDL - Decoder

-

تست بنچ VHDL – دیکودر VHDL Test Bench - Decoder

-

سنتز – دیکودر Synthesis - Decoder

-

شبیه سازی رفتاری – دیکودر Behavioral Simulation - Decoder

-

VHDL – انکودر VHDL - Encoder

-

تست بنچ VHDL – انکودر VHDL Test Bench - Encoder

-

سنتز و شبیه سازی رفتاری – انکودر Synthesis & Behavioral Simulation - Encoder

-

کد VHDL اصلاح شده – انکودر Modified VHDL Code - Encoder

-

VHDL – D Latch VHDL - D Latch

یادگیری سریع: بخش های 8 و 10 (استفاده از ساختار when-else) Fast Track Learning : Sections 8 & 10 ( Using when-else construct )

-

یادگیری سریع: VHDL (منطق ترکیبی – با استفاده از when else) Fast Track : VHDL ( Combinational Logic - using when else )

-

سنتز: منطق های ترکیبی Synthesis : Combinational Logics

-

یادگیری سریع: تست بنچ (منطق های ترکیبی) Fast Track : Test Bench ( Combinational Logics)

-

شبیه سازی رفتاری – منطق های ترکیبی Behavioral Simulation - Combinational Logics

بلاک های دیجیتال محاسباتی – کد VHDL، تست بنچ، سنتز و اعتبارسنجی Arithmetic Digital Blocks -VHDLCode ,TestBench , Synthesis & Verification

-

VHDL – نیم جمع کننده VHDL - Half Adder

-

تست بنچ VHDL – نیم جمع کننده VHDL Test Bench - Half Adder

-

سنتز و شبیه سازی رفتاری – نیم جمع کننده Synthesis & Behavioral Simulation - Half Adder

-

VHDL – تمام جمع کننده VHDL - Full Adder

-

تست بنچ – تمام جمع کننده Test Bench - Full Adder

-

سنتز – تمام جمع کننده Synthesis - Full Adder

-

شبیه سازی رفتاری – تمام جمع کننده Behavioral Simulation - Full Adder

سبک مدل سازی VHDL – مدل سازی رفتاری VHDL Modeling Style - Behavioral Modeling

-

مدل سازی رفتاری VHDL – مقایسه کننده 4 بیتی VHDL Behavioral Modeling - 4 Bit Comparator

-

تست بنچ – مقایسه کننده 4 بیتی (مدل سازی رفتاری) Test Bench - 4 Bit Comparator ( Behavioral Modeling )

-

سنتز و شبیه سازی رفتاری – مقایسه کننده 4 بیتی (مدل سازی رفتاری) Synthesis & Behavioral Simulation - 4 Bit Comparator ( Behavioral Modeling )

سبک مدل سازی VHDL – مدل سازی DataFlow VHDL Modeling Style - DataFlow Modeling

-

مدل سازی DataFlow VHDL – مقایسه کننده 4 بیتی VHDL DataFlow Modeling - 4 Bit Comparator

-

تست بنچ VHDL – مقایسه کننده 4 بیتی (مدل سازی Data Flow) VHDL Test Bench - 4 Bit Comparator ( Data Flow Modeling )

-

سنتز و شبیه سازی رفتاری – مقایسه کننده 4 بیتی (مدل سازی Data Flow) Synthesis & Behavioral Simulation - 4 Bit Comparator ( Data Flow Modeling )

سبک مدل سازی VHDL – مدل سازی ساختاری VHDL Modeling Style - Structural Modeling

-

VHDL – مدل سازی ساختاری (مقایسه کننده 4 بیتی) VHDL - Structural Modeling ( 4 Bit Comparator )

-

تست بنچ VHDL – مقایسه کننده 4 بیتی (مدل سازی ساختاری) VHDL Test Bench - 4 Bit Comparator ( Structural Modeling )

-

سنتز و شبیه سازی رفتاری – مقایسه کننده 4 بیتی (مدل سازی ساختاری) Synthesis & Behavioral Simulation - 4 Bit Comparator ( Structural Modeling )

بلاک های منطقی ترتیبی – کد VHDL، تست بنچ، سنتز و اعتبارسنجی (FPGA) Sequential Logic Blocks - VHDL Code , TestBench,Synthesis & Verification (FPGA)

-

VHDL – D فلیپ فلاپ VHDL - D FlipFlop

-

تست بنچ VHDL – D فلیپ فلاپ VHDL Test Bench - D Flipflop

-

سنتز و شبیه سازی رفتاری – D فلیپ فلاپ Synthesis & Behavioral Simulation - D Flipflop

-

VHDL – D فلیپ فلاپ با ریست غیرهمزمان VHDL - D FlipFlop With Asynchronous Reset

-

VHDL – D فلیپ فلاپ با ریست همزمان VHDL - D FlipFlop With Synchronous Reset

VHDL – طراحی منطقی همزمان – قسمت 1 (طراحی شمارنده بالا و شمارنده پایین) VHDL - Synchronous Logic Design - Part 1 ( Up Counter & Down Counter Design )

-

VHDL – شمارنده باینری بالا VHDL - Binary Up Counter

-

تست بنچ – شمارنده باینری بالا Test Bench - Binary Up Counter

-

سنتز و شبیه سازی رفتاری – شمارنده باینری بالا Synthesis & Behavioral Simulation - Binary Up Counter

-

VHDL – شمارنده باینری پایین با تست بنچ، سنتز و شبیه سازی VHDL - Binary Down Counter with Test Bench , Synthesis & Simulation

VHDL – طراحی منطقی همزمان – قسمت 2 (طراحی های شمارنده بالا-پایین باینری) VHDL - Synchronous Logic Design - Part 2 ( Binary Up-Down Counter Designs )

-

VHDL – شمارنده 4 بیتی باینری بالا-پایین (همزمان) VHDL - 4 Bit Binary Up-Down Counter ( Synchronous )

-

سنتز – شمارنده 4 بیتی باینری بالا-پایین (همزمان) Synthesis - 4 bit Binary Up-Down counter ( Synchronous )

-

تست بنچ VHDL – شمارنده باینری بالا-پایین VHDL Test Bench - Binary Up-Down Counter

-

شبیه سازی رفتاری – شمارنده باینری بالا-پایین (4 بیتی – همزمان) Behavioral Simulation- Binary Up-Down Counter ( 4 Bit - Synchronous )

VHDL – طراحی منطقی همزمان – قسمت 3 (شمارنده بالا – پایین باینری بهبود یافته) VHDL - Synchronous Logic Design - Part 3 ( Improved Binary Up - Down Counter )

-

VHDL – شمارنده بالا-پایین باینری بهبود یافته (4 بیتی – همزمان) VHDL - Improved Binary Up-Down Counter ( 4 bit - Synchronous )

-

سنتز – شمارنده بالا-پایین باینری بهبود یافته Synthesis - Improved Binary Up-Down Counter

-

شبیه سازی رفتاری – شمارنده بالا-پایین باینری بهبود یافته Behavioral Simulation - Improved Binary Up-Down Counter

اعمال محدودیت های قفل کردن پین Applying Pin Locking Constraints

-

محدودیت های فیزیکی – محدودیت های قفل کردن پین Physical Constraints - Pin Locking Constraints

اعمال محدودیت های زمان بندی Applying Timing Constraints

-

محدودیت های زمان بندی – شمارنده 4 بیتی باینری بالا-پایین Timing Constraints - 4 Bit Binary Up-Down Counter

پیاده سازی طراحی – Xilinx FPGA Design Implementation - Xilinx FPGA

-

شبیه سازی زمان بندی پس از مسیریابی (زمان بندی استاتیک) Post Route Timing Simulation( Static Timing )

VHDL – طراحی منطقی همزمان – قسمت 4 (طراحی شمارنده بالا-پایین Gray) VHDL - Synchronous Logic Design - Part 4 ( Gray Up-Down Counter Design )

-

VHDL – شمارنده بالا-پایین Gray VHDL - Gray Up-Down Counter

-

سنتز: شمارنده بالا-پایین Gray Synthesis : Gray Up-Down Counter

-

تست بنچ – شمارنده بالا-پایین Gray Test Bench - Gray Up-Down Counter

-

شبیه سازی رفتاری – شمارنده بالا-پایین Gray Behavioral Simulation - Gray Up-Down Counter

VHDL – طراحی منطقی همزمان – قسمت 5 (ثبات شیفت SISO) (Xilinx FPGA) VHDL - Synchronous Logic Design - Part 5 ( SISO Shift Register ) ( Xilinx FPGA )

-

VHDL – ثبات شیفت سریال ورودی سریال خروجی (SISO) VHDL - Serial In Serial Out Shift Register ( SISO )

-

سنتز – ثبات شیفت SISO Synthesis - SISO Shift Register

-

تست بنچ VHDL – ثبات شیفت SISO VHDL Test Bench - SISO Shift Register

-

شبیه سازی رفتاری – ثبات شیفت SISO Behavioral Simulation - SISO Shift Register

VHDL – طراحی منطقی همزمان – قسمت 6 (ثبات شیفت SIPO) (Xilinx FPGA) VHDL - Synchronous Logic Design - Part 6 ( SIPO Shift Register ) ( Xilinx FPGA)

-

VHDL – ثبات شیفت سریال ورودی موازی خروجی (SIPO) VHDL - Serial In Parallel Out Shift Register ( SIPO )

-

سنتز – ثبات شیفت SIPO Synthesis - SIPO Shift Register

-

تست بنچ VHDL – ثبات شیفت SIPO VHDL Test Bench - SIPO Shift Register

-

شبیه سازی رفتاری – ثبات شیفت SIPO Behavioral Simulation - SIPO Shift Register

VHDL – طراحی منطقی همزمان – قسمت 7 (ثبات شیفت PISO) (Xilinx FPGA) VHDL - Synchronous Logic Design - Part 7 ( PISO Shift Register ) ( Xilinx FPGA )

-

VHDL – ثبات شیفت موازی ورودی سریال خروجی VHDL - Parallel In Serial Out Shift Register

-

سنتز – ثبات شیفت PISO Synthesis - PISO Shift Register

-

تست بنچ VHDL – ثبات شیفت PISO VHDL Test Bench - PISO Shift Register

-

شبیه سازی رفتاری – ثبات شیفت PISO Behavioral Simulation - PISO Shift Register

VHDL – طراحی منطقی همزمان – قسمت 8 (ثبات شیفت PIPO) (Xilinx FPGA) VHDL - Synchronous Logic Design - Part 8 ( PIPO Shift Register ) ( Xilinx FPGA )

-

VHDL – ثبات شیفت موازی ورودی موازی خروجی VHDL - Parallel In Parallel Out Shift Register

-

سنتز – ثبات شیفت PIPO Synthesis - PIPO Shift Register

-

تست بنچ VHDL – ثبات شیفت PIPO VHDL Test Bench - PIPO Shift Register

-

شبیه سازی رفتاری – ثبات شیفت PIPO Behavioral Simulation - PIPO Shift Register

درباره طراحی ماشین حالت – FSM ها: پیاده سازی آشکارساز توالی About State Machine Design - FSMs : Sequence Detector Implementtion

-

طراحی ماشین حالت – Moore FSM و Mealy FSM برای آشکارساز توالی: State Machine Design- Moore FSM & Mealy FSM for Sequence Detector :

طراحی ماشین حالت VHDL – Moore FSM برای آشکارساز توالی VHDL State Machine Design - Moore FSM for Sequence Detector

-

طراحی VHDL Moore FSM: مثال آشکارساز توالی Moore FSM VHDL Design : Sequence Detector Example

-

سنتز: Moore FSM: آشکارساز توالی Synthesis : Moore FSM : Sequence Detector

-

تست بنچ: Moore FSM: آشکارساز توالی Test Bench : Moore FSM : Sequence Detector

-

شبیه سازی: Moore FSM: آشکارساز توالی Simulation : Moore FSM : Sequence Detector

طراحی ماشین حالت VHDL – Mealy FSM برای آشکارساز توالی VHDL State Machine Design - Mealy FSM for Sequence Detector

-

VHDL: مثال Mealy FSM: آشکارساز توالی VHDL : Mealy FSM Example : Sequence Detector

-

سنتز: مثال Mealy FSM: آشکارساز توالی Synthesis : Mealy FSM Example : Sequence Detector

-

تست بنچ: مثال Mealy FSM: آشکارساز توالی Test Bench : Mealy FSM Example : Sequence Detector

-

شبیه سازی: مثال Mealy FSM: آشکارساز توالی Simulation : Mealy FSM Example : Sequence Detector

درباره طراحی ماشین حالت – FSM ها: پیاده سازی شمارنده بالا/پایین باینری About State Machine Design - FSMs : Binary Up/Down Counter Implementation

-

طراحی های ماشین حالت برای شمارنده ها State Machine Designs for Counters

طراحی ماشین حالت Moore (FSM): شمارنده بالا/پایین باینری Moore State Machine ( FSM ) Design : Binary Up/Down Counter

-

VHDL – Moore FSM: طراحی شمارنده بالا/پایین باینری VHDL - Moore FSM : Binary Up/Down Counter Design

-

سنتز – Moore FSM: شمارنده بالا/پایین باینری Synthesis - Moore FSM : Binary Up/Down Counter

-

تست بنچ – Moore FSM: شمارنده بالا/پایین باینری Test Bench - Moore FSM : Binary Up/Down Counter

-

شبیه سازی – Moore FSM: شمارنده بالا/پایین باینری Simulation - Moore FSM : Binary Up/Down Counter

-

تغییر از نوع داده Enumerated به Integer Changing from Enumerated to Integer Data Type

طراحی ماشین حالت Mealy (FSM): شمارنده بالا/پایین باینری Mealy State Machine ( FSM ) Design : Binary Up/Down Counter

-

VHDL: Mealy FSM: طراحی شمارنده بالا/پایین باینری VHDL : Mealy FSM : Binary Up/Down Counter Design

-

سنتز: Mealy FSM: شمارنده بالا/پایین باینری Synthesis : Mealy FSM : Binary Up/Down Counter

-

تست بنچ: Mealy FSM: شمارنده بالا/پایین باینری Test Bench : Mealy FSM : Binary Up/Down Counter

-

شبیه سازی: Mealy FSM: شمارنده بالا/پایین باینری Simulation : Mealy FSM : Binary Up/Down Counter

FSM - ماشین حالت محدود برای شمارنده بالا/پایین Gray FSM - Finite State Machine for Gray Up/Down Counter

-

VHDL: FSM برای شمارنده بالا/پایین Gray VHDL : FSM for Gray Up/Down Counter

-

سنتز: شمارنده بالا/پایین Gray Synthesis : Gray Up/Down Counter

-

اعمال محدودیت ها بر FSM شمارنده بالا پایین Gray Applying Constraints to FSM Gray Updown Counter

-

تست بنچ VHDL: شمارنده بالا/پایین Gray VHDL Test Bench : Gray Up/Down Counter

-

شبیه سازی رفتاری - FSM شمارنده بالا-پایین Gray Behavioral Simulation - FSM Gray Up-Down Counter

استفاده از ساختار Generate Using Generate Construct

-

VHDL: استفاده از Generate برای ثبات شیفت N بیتی VHDL : Using Generate for N- Bit Shift Register

-

سنتز: ثبات شیفت N بیتی با استفاده از ساختار Generate Synthesis : N-Bit Shift Register using Generate Construct

-

تست بنچ: ثبات شیفت N بیتی با استفاده از ساختار Generate Test Bench : N - Bit Shift Register using Generate Construct

-

شبیه سازی: ثبات شیفت N بیتی با استفاده از ساختار Generate Simulation : N Bit Shift Register using Generate Construct

استفاده از ساختار Block Using Block Construct

-

VHDL: طراحی دیجیتال با استفاده از ساختار Block VHDL : Digital Design Using Block Construct

-

سنتز: طراحی دیجیتال با استفاده از ساختار Block Synthesis : Digital Design Using Block Construct

درباره زیربرنامه - Function و Procedure About Subprogram - Function & Procedure

-

زیربرنامه - Function و Procedure SubProgram - Function & Procedure

استفاده از زیربرنامه: Function Using SubProgram : Function

-

VHDL: استفاده از Function برای طراحی جمع کننده N بیتی VHDL : Using Function for N-Bit Adder Design

-

سنتز: استفاده از Function برای طراحی جمع کننده N بیتی Synthesis : Using Function for N-Bit Adder Design

-

تست بنچ: استفاده از Function برای طراحی جمع کننده N بیتی Test Bench : Using Function for N-Bit Adder Design

-

شبیه سازی: استفاده از Function برای طراحی جمع کننده N بیتی Simulation : Using Function for N-Bit Adder Design

استفاده از زیربرنامه - Procedure Using SubProgram - Procedure

-

VHDL: استفاده از Procedure برای طراحی جمع کننده N بیتی VHDL : Using Procedure for N-Bit Adder Design

-

سنتز: استفاده از Procedure برای طراحی جمع کننده N بیتی Synthesis : Using Procedure for N-Bit Adder Design

-

تست بنچ: استفاده از Procedure برای طراحی جمع کننده N بیتی Test Bench : Using Procedure for N-Bit Adder Design

-

شبیه سازی: استفاده از Procedure برای طراحی جمع کننده N بیتی Simulation : Using Procedure for N-Bit Adder Design

طراحی ضرب کننده Multiplier Design

-

VHDL: ضرب کننده باینری VHDL : Binary Multiplier

VHDL - (Xilinx FPGA) طراحی A.L.U. (واحد محاسبات و منطق) VHDL - ( Xilinx FPGA ) A.L.U. Design ( Arithmetic & Logic Unit )

-

VHDL - طراحی ALU (رفتاری) VHDL - ALU Design ( Behavioral )

-

سنتز - ALU Synthesis - ALU

-

تست بنچ VHDL - ALU VHDL Test Bench - ALU

-

شبیه سازی رفتاری - ALU Behavioral Simulation - ALU

VHDL(Xilinx FPGA) طراحی حافظه – طراحی واحد ROM VHDL(Xilinx FPGA) Memory Design-ROM Unit Design

-

VHDL - طراحی واحد ROM VHDL - ROM Unit Design

-

تست بنچ VHDL - واحد ROM VHDL Test Bench - ROM Unit

-

سنتز - واحد ROM Synthesis - ROM Unit

-

شبیه سازی رفتاری - واحد ROM Behavioral Simulation - ROM Unit

VHDL(Xilinx FPGA) طراحی حافظه – طراحی واحد RAM VHDL(Xilinx FPGA) Memory Design-RAM Unit Design

-

VHDL - طراحی واحد RAM VHDL - RAM Unit Design

-

تست بنچ VHDL - واحد RAM VHDL Test Bench - RAM Unit

-

سنتز - واحد RAM Synthesis - RAM Unit

-

شبیه سازی رفتاری - واحد RAM Behavioral Simulation - RAM Unit

تکنیک هایی برای ادغام پروژه VHDL (Xilinx FPGA) Techniques for Integrating VHDL Project (Xilinx FPGA)

-

VHDL- منطق اول VHDL- Logic 1st

-

VHDL - منطق دوم VHDL - Logic 2nd

-

VHDL - ادغام پروژه VHDL - Project Integration

-

تست بنچ VHDL - پروژه یکپارچه VHDL Test Bench - Integrated Project

گزینه های شغلی: بررسی اجمالی Career Options : Overview

-

گزینه های شغلی در برنامه نویسی VHDL، طراحی FPGA – بررسی اجمالی Career Options in VHDL Programming , FPGA Design - Overview

شروع با اصول اولیه PCB و طراحی PCB Starting with the Basics of PCB & PCB Design

-

مقدمه ای بر PCB و طراحی PCB Introduction to PCB & PCB Design

-

مقدمه ای بر برد PCB Introduction to PCB Board

-

قطعات الکترونیکی و ابعاد/Footprint ها Electronic Components & Dimensions / Footprints

ویژگی های نرم افزار طراحی PCB EasyEDA Features of EasyEDA PCB Design Software Tool

-

ایجاد حساب کاربری خود برای دسترسی به نرم افزار آنلاین طراحی PCB EasyEDA Create your Account to Access EasyEDA PCB Design OnLine Software

-

مقدمه: ویژگی های نرم افزار طراحی PCB EasyEDA Introduction : Features of EasyEDA PCB Design Software Tool

اولین پروژه طراحی PCB با جریان طراحی پایه First PCB Design Project with Basic Design Flow

-

مثال اولین پروژه طراحی PCB: جریان طراحی پایه First PCB Design Project Example : Basic Design Flow

-

مبانی: قرار دادن قطعات (Layout PCB) و مسیریابی Track (طراحی PCB) Basics : Component Placement ( PCB Layout ) & Track Routing ( PCB Design )

طراحی شماتیک - برای PCB تک لایه Schematic Design - For Single Layer PCB

-

طراحی شماتیک - منبع تغذیه DC دوگانه Schematic Design - Dual DC Power Supply

-

اضافه کردن جزئیات به طراحی شماتیک Adding Details to Schematic Design

قرار دادن قطعات در یک طراحی PCB Component Placement in a PCB Design

-

رهنمودهای قرار دادن قطعات برای طراحی PCB 1 لایه Component Placement Guidelines for 1 Layer PCB Design

-

قرار دادن قطعات (Layout PCB): منبع تغذیه DC دوگانه Component Placement ( PCB Layout ) : Dual DC Power Supply

مسیریابی Track در یک طراحی PCB Track Routing in a PCB Design

-

رهنمودهای مسیریابی Track برای PCB 1 لایه Track Routing Guidelines for 1 - Layer PCB

-

روش های مسیریابی Track در طراحی PCB Track Routing Methods in PCB Design

مسیریابی Track - طراحی PCB تک لایه Track Routing - Single Layer PCB Design

-

طراحی PCB تک لایه (مسیریابی Track) Single Layer PCB Design ( Track Routing )

اتصال به زمین در طراحی PCB Grounding in PCB Design

-

تکنیک های اتصال به زمین در طراحی PCB 1 لایه Grounding Techniques in 1 Layer PCB Design

بررسی قوانین طراحی Design Rule Check

-

DRC - بررسی قوانین طراحی DRC - Design Rule Check

ویژگی Cross Probing Cross Probing Feature

-

Cross Probing در طراحی PCB Cross Probing in PCB Design

ویژگی Auto Router Auto Router Feature

-

Auto Router برای طراحی PCB 1 لایه Auto Router for 1 Layer PCB Design

طراحی PCB تک لایه (SMT - Surface Mount) Single Layer ( SMT - Surface Mount ) PCB Design

-

طراحی شماتیک - برای طراحی PCB SMT تک لایه Schematic Design - For Single Layer SMT PCB Design

-

قرار دادن قطعات: طراحی PCB SMT تک لایه Component Placement : Single Layer SMT PCB Design

-

مسیریابی Track - طراحی PCB SMT تک لایه Track Routing - Single Layer SMT PCB Design

طراحی PCB نوع Single Layer SMT به Through Version Designing Single Layer SMT to Through Version Type PCB

-

طراحی یک نسخه جدید: از Single Layer SMT به PCB نوع Through Hole Designing a New Version : From Single Layer SMT to Through Hole Type PCB

پروژه طراحی PCB با استفاده مستقیم از ابزار PCB (بدون استفاده از ابزار شماتیک) PCB Design Project with Directly using PCB Tool ( Without using Schematic Tool )

-

ایجاد یک پروژه طراحی PCB بدون استفاده از ابزار شماتیک Creating a PCB Design Project without using Schematic Tool

PCB Artwork و راه اندازی ساخت PCB کوچک برای PCB تک لایه PCB Artwork & Small PCB Fabrication Setup for Single Layer PCB

-

PCB Artwork PCB Artwork

-

لایه پوشش لحیم (Solder Mask) Solder Mask Layer

-

لایه Silk Screen (Legend) Silk Screen Layer ( Legend )

-

درباره راه اندازی ساخت PCB کوچک (برای PCB 1 لایه) About Small PCB Fabrication Setup ( For 1 Layer PCB )

طراحی PCB دو طرفه: مطالعه موردی پایه Double Sided PCB Design : Basic Case Study

-

طراحی شماتیک: برای PCB دو طرفه Schematic Design : For Double Sided PCB

-

قرار دادن قطعات Component Placement

-

مسیریابی Track: PCB دو لایه / دو طرفه Track Routing : Double Layer / Double Sided PCB

https://donyad.com/d/6d034c

Pravinkumar Ambekar

Pravinkumar Ambekar

Electronics Circuit Designer، Developer، Programmer & Trainer. Pravinkumar P. Ambekar ، مدرس با M.Tech واجد شرایط است. - مدرک کارشناسی ارشد در فناوری طراحی الکترونیک از مرکز طراحی و فناوری الکترونیک هند. او 22+ سال تجربه پس از M.Tech دارد. در حوزه طراحی مدار الکترونیکی ، برنامه نویسی ، سیستم جاسازی شده ، VLSI - FPGA / CPLD ، PSOC ، PLC ، طراحی PCB اعمال شده در آموزش ، پروژه های صنعتی ، پروژه های دفاعی / توسعه محصول. او دارای تجربه کار بر روی سیستم عامل های مختلف و ابزارهای EDA / نرم افزارهای برنامه نویسی است که شامل VLSI - VHDL و Verilog Programming برای Xilinx FPGAs ، CPLD ها با استفاده از Xilinx ISE Tool / Xilinx Vivado Tool ، برنامه نویسی PSOC1 با استفاده از Cypress PSOC طراح و برنامه نویسی PSOC3 / PSOC4 با استفاده از Cypress PSOC سازنده ، برنامه نویسی برای میکروکنترلرهای خانواده MCS-51 (8051) با استفاده از Keil uVision 4 ، میکروکنترلرهای برنامه نویسی Atmel (AVR) - ATMega 16/32/128 با استفاده از Atmel AVR Studio ، برنامه نویسی Microchip PIC 16/18 میکروکنترلرها با استفاده از MPLAB ، آردوینو برای Arduino تابلوهای Uno ، برنامه نویسی MSP430 Board of Texas Instruments with Energia، Raspberry Pi & Raspbian Linux، Python Programming with Python 3.8 (IDLE)، Python Thonny، Python Pycharm، Anaconda Navigator - Jupyter Notebook، Spyder Python، Google Colab، Crouzet Millenium 3 for Google برنامه نویسی ، FBD و همچنین طراحی PCB که شامل نرم افزارهای PCB مانند EasyEDA ، Eagle ، KiCad 5.1 ، Fritzing & Express PCB است.

نمایش نظرات