آموزش Verilog HDL: VLSI Hardware Design Comprehensive Masterclass - آخرین آپدیت

Verilog HDL: VLSI Hardware Design Comprehensive Masterclass

یک دوره جامع شغل محور در مورد طراحی منطق برای سخت افزار با استفاده از زبان توصیف سخت افزار Verilog.

سبک و رویکرد ساختاری منحصربهفرد، آزمایششده و اثباتشده دنبال شد.

ترکیب متفکرانه تئوری و عمل برای یادگیری شما.

پشتیبانی نامحدود با مربی.

تمام جزئیات پیچیده در تفکر و درک طراحی سخت افزار را درک کنید.

اصول با مثال های متعدد تقویت می شوند.

دستورالعملهای کدنویسی خوب و مثالهای بدی که باید از آنها اجتناب کنید.

پس از اتمام دوره، میتوانید با اطمینان کدهای قابل ترکیب برای طراحی سختافزار پیچیده بنویسید.

بحث کامل در مورد طراحی هر قطعه سخت افزاری.

توضیح مفصل رابطه بین کد و واحدهای سخت افزار دیجیتال.

بیش از 100 نمونه کد و میزهای آزمایشی مورد استفاده در دوره را رایگان دانلود کنید.

دسترسی به همه مواد و ارتقاءهای آینده.

آزمونها و تکالیف بارگیری می شود تا درک شما را بررسی کند.

دروس را با سرعت خود کار کنید.

معرفی Introduction

-

معرفی Introduction

-

پوشش دوره Course coverage

-

بررسی مفاهیم VLSI Review of VLSI concepts

-

اصول اولیه CMOS سریع (به درخواست اضافه شده است) Quick CMOS basics (added as per request)

-

VLSI چیست؟ What is VLSI?

-

بررسی شرایط Review of terms

-

حداقل اندازه ویژگی Minimum feature size

-

چرا ادغام؟ Why Integration?

-

مناطق وسیع در VLSI Broad areas in VLSI

-

سبک های طراحی VLSI - سفارشی کامل VLSI Design Styles - Full Custom

-

سبک های طراحی VLSI - نیمه سفارشی VLSI Design Styles - Semi Custom

-

سبک های طراحی VLSI - FPGA VLSI Design Styles - FPGA

-

سبک های طراحی VLSI - آرایه دروازه VLSI Design Styles - Gate Array

-

سبک های طراحی VLSI - مقایسه VLSI Design Styles - Comparison

-

سفارشی کامل در مقابل نیمه سفارشی Full custom vs Semi custom

-

ASIC در مقابل FPGA ASIC vs FPGA

-

جریان طراحی ASIC - قسمت 1 ASIC Design Flow - Part 1

-

جریان طراحی ASIC - قسمت 2 ASIC Design Flow - Part 2

-

جریان طراحی ASIC - مشخصات طراحی ASIC Design Flow - Design Specs

-

جریان طراحی ASIC - معماری ASIC Design Flow - Architecturing

-

جریان طراحی ASIC - کدگذاری RTL ASIC Design Flow - RTL coding

-

جریان طراحی ASIC - تأیید ASIC Design Flow - Verification

-

جریان طراحی ASIC - سنتز ASIC Design Flow - Synthesis

-

جریان طراحی ASIC - طراحی برای آزمایش پذیری ASIC Design Flow - Design for Testability

-

جریان طراحی ASIC - تجزیه و تحلیل زمان ASIC Design Flow - Timing Analysis

-

جریان طراحی ASIC - برنامه ریزی کف، قرار دادن و مسیریابی ASIC Design Flow - Floorplanning, Placement & Routing

-

جریان طراحی ASIC - تأیید رسمی ASIC Design Flow - Formal Verification

-

جریان طراحی ASIC - برآورد توان ASIC Design Flow - Power Estimation

-

جریان طراحی ASIC - ساخت ASIC Design Flow - Fabrication

-

جریان طراحی ASIC - بسته بندی ASIC Design Flow - Packaging

مبانی Verilog Verilog Basics

-

سبک های طراحی Verilog Verilog Design Styles

-

اولین طراحی سبک جریان داده من My First Dataflow Style Design

-

اولین طراحی به سبک رفتاری من My First Behavioral Style Design

-

اولین طراحی من به سبک ساختاری My First Structural Style Design

-

جمع کننده کامل 1 بیتی (Sturctural-1) 1-bit Full Adder (Sturctural-1)

-

جمع کننده کامل 1 بیتی (Sturctural-2) 1-bit Full Adder (Sturctural-2)

-

جمع کننده کامل 1 بیتی (Sturctural-3) 1-bit Full Adder (Sturctural-3)

-

جمع کننده کامل 1 بیتی (جریان داده) 1-bit Full Adder (Dataflow)

-

جمع کننده کامل 1 بیتی (رفتاری) 1-bit Full Adder (Behavioral)

-

اولین نیمکت تست من My first Test Bench

طراحی منطق ترکیبی Designing Combinational Logic

-

4 منطق ارزشی 4 Valued Logic

-

انواع داده ها Data Types

-

نمایندگی شماره Number Representation

-

بیت و اتوبوس Bit and Bus

-

قراردادهای نامگذاری Naming Conventions

-

اپراتورها - Bitwise Operators - Bitwise

-

اپراتورها - حساب Operators - Arithmetic

-

اپراتورها - منطقی Operators - Logical

-

اپراتورها - رابطه ای Operators - Relational

-

اپراتورها - کاهش Operators - Reduction

-

اپراتورها - Shift Operators - Shift

-

اپراتورها - الحاق Operators - Concatenation

-

اپراتورها - تکرار Operators - Repetition

-

اپراتورها - مشروط Operators - Conditional

-

جدول وضوح خروجی Output Resolution Table

-

جمع کننده کامل 4 بیتی (ساختاری) 4-bit Full Adder (Structural)

-

جمع کننده کامل 4 بیتی (جریان داده) 4-bit Full Adder (Dataflow)

-

جمع کننده کامل 4 بیتی (رفتاری) 4-bit Full Adder (Behavioral)

-

میز تست کامل جمع کننده 4 بیتی 4-bit Full Adder Test Bench

-

مولتی پلکسر 2:1 (جریان داده) 2:1 Multiplexer (Dataflow)

-

مولتی پلکسر 2:1 (رفتاری) 2:1 Multiplexer (Behavioral)

-

مولتی پلکسر 4:1 (Dataflow1) 4:1 Multiplexer (Dataflow1)

-

مولتی پلکسر 4:1 (Dataflow2) 4:1 Multiplexer (Dataflow2)

-

مولتی پلکسر 4:1 (Dataflow3) 4:1 Multiplexer (Dataflow3)

-

مولتی پلکسر 4:1 (رفتاری) 4:1 Multiplexer (Behavioral)

-

رسیور 2 X 4 (جریان داده) 2 X 4 Decoder (Dataflow)

-

رسیور 2 X 4 (رفتاری) 2 X 4 Decoder (Behavioral)

-

رسیور 3 X 8 (جریان داده) 3 X 8 Decoder (Dataflow)

-

رمزگذار 4 X 2 (جریان داده) 4 X 2 Encoder (Dataflow)

-

رمزگذار 4 X 2 (رفتاری) 4 X 2 Encoder (Behavioral)

-

رمزگذار اولویت 4 X 2 (رفتاری) 4 X 2 Priority Encoder (Behavioral)

-

رمزگذار اولویت 4 X 2 (جریان داده) 4 X 2 Priority Encoder (Dataflow)

-

مقایسه کننده 4 بیتی (جریان داده 1) 4-bit Comparator (Dataflow 1)

-

مقایسه کننده 4 بیتی (جریان داده 2) 4-bit Comparator (Dataflow 2)

-

مقایسه کننده 4 بیتی (رفتاری) 4-bit Comparator (Behavioral)

-

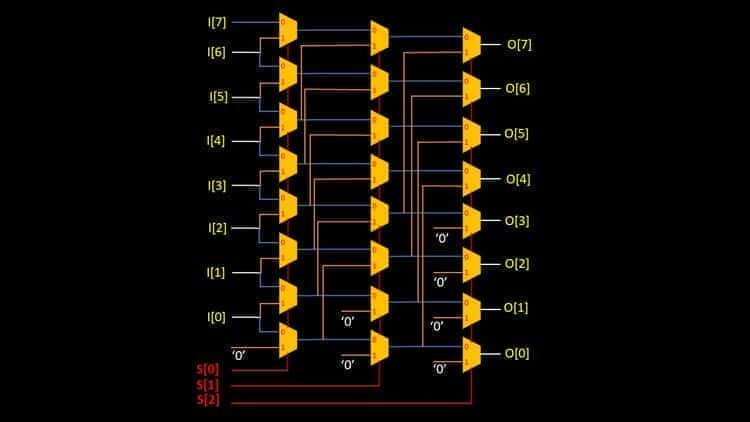

شیفتر بشکه ای 8 بیتی (ترکیبی چپ و راست) 8-bit Barrel Shifter (Combinational Left & Right)

-

طراحی واحد حساب و منطق (ALU) Designing Arithmetic & Logic Unit (ALU)

طراحی منطق ترتیبی Designing Sequential Logic

-

ساعت، D-Latch و D-Flip Flop Clock, D-Latch and a D-Flip Flop

-

D-Flip Flop در مقابل D-Latch D-Flip Flop vs D-Latch

-

D-Latch (جریان داده) D-Latch (Dataflow)

-

D-Latch (رفتاری) D-Latch (Behavioral)

-

D-Latch با تنظیم مجدد ناهمزمان (رفتاری) D-Latch with Asynchronous Reset (Behavioral)

-

D-Flip Flop (پایه) D-Flip Flop (Basic)

-

D-Flip Flop فعال شده با لبه مثبت با بازنشانی فعال ناهمزمان بالا Postitive Edge Triggered D-Flip Flop with Asynchronous Active High Reset

-

D-Flip Flop با لبه منفی با بازنشانی فعال ناهمزمان بالا Negative Edge Triggered D-Flip Flop with Asynchronous Active High Reset

-

D-Flip Flop فعال شده با لبه مثبت با بازنشانی پایین فعال ناهمزمان Postitive Edge Triggered D-Flip Flop with Asynchronous Active Low Reset

-

D-Flip Flop با لبه مثبت با ست بالا فعال ناهمزمان Postitive Edge Triggered D-Flip Flop with Asynchronous Active High Set

-

D-Flip Flop همزمان با تنظیم مجدد فعال بالا Synchronous D-Flip Flop with Active High Reset

-

D-Flip Flop همزمان با تنظیم مجدد فعال پایین Synchronous D-Flip Flop with Active Low Reset

-

D-Flip Flop همزمان با تنظیم مجدد و تنظیم مجدد Synchronous D-Flip Flop with Reset and Set

-

طراحی تنظیم مجدد همزمان و ناهمزمان Synchronous and Asynchronous Reset Design

-

مجموعه ثبت دوقلو 8 بیتی 8-bit Twin Register Set

-

طراحی شیفت رجیستر 5 بیتی از چپ به راست Designing a 5-bit Left to Right Shift Register

-

طراحی یک شیفت رجیستر جهانی 5 بیتی Designing a 5-bit Universal Shift Register

-

طراحی یک شمارنده اولیه Designing a basic counter

-

نوشتن نیمکت تست برای پیشخوان Writing a Test Bench for a Counter

-

طراحی یک شمارنده بالا با آپشن بار Designing an Up Counter with Load Option

-

طراحی یک شمارنده بالا یا پایین Designing an Up or Down Counter

-

طراحی یک شمارنده مدول Designing a Modulus Counter

-

طراحی Range Up Counter Designing a Range Up Counter

-

طراحی یک شمارنده دامنه بالا یا پایین با گزینه بار Designing a Range Up or Down Counter with Load Option

-

طراحی تقسیم کننده فرکانس ساعت (تقسیم بر 2) Designing a Clock Frequency Divider (Divide by 2)

-

طراحی تقسیم کننده فرکانس ساعت (تقسیم بر 4) Designing a Clock Frequency Divider (Divide by 4)

-

طراحی یک تقسیم کننده فرکانس ساعت (تقسیم بر 3) Designing a Clock Frequency Divider (Divide by 3)

-

طراحی یک ساعت منفرد در اولین خروجی (FIFO) Designing a Single Clock First In First Out (FIFO)

-

طراحی یک ساعت دوگانه در اولین خروجی (FIFO) Designing a Dual Clock First In First Out (FIFO)

طراحی خاطرات Designing Memories

-

گزینه ها و تعاریف آرایه حافظه Memory Array Options and Definitions

-

رم تک پورت - v1 Single Port Ram - v1

-

رم تک پورت - نسخه 2 Single Port Ram - v2

-

رم تک پورت - نسخه 3 Single Port Ram - v3

-

رم تک پورت - نسخه 4 Single Port Ram - v4

-

رم دو پورت - نسخه 1 Dual Port Ram - v1

-

دو پورت رم - نسخه 2 Dual Port Ram - v2

-

True Dual Port Ram - v1 True Dual Port Ram - v1

-

True Dual Port Ram - v2 True Dual Port Ram - v2

طراحی ماشین های حالت محدود Designing Finite State Machines

-

میلی در مقابل ماشین مور Mealy vs Moore Machine

-

Mealy - 101 آشکارساز توالی غیر همپوشانی Mealy - 101 Non-Overlapping Sequence Detector

-

Mealy - 011 Non-Overlapping Sequence Detector Mealy - 011 Non-Overlapping Sequence Detector

-

Mealy - 000 آشکارساز توالی غیر همپوشانی Mealy - 000 Non-Overlapping Sequence Detector

-

Mealy - 0101 Non-Overlapping Sequence Detector Mealy - 0101 Non-Overlapping Sequence Detector

-

Mealy - 11011 Non-Overlapping Sequence Detector Mealy - 11011 Non-Overlapping Sequence Detector

-

Mealy - 101 آشکارساز توالی همپوشانی Mealy - 101 Overlapping Sequence Detector

-

Mealy - 011 ردیاب توالی همپوشانی Mealy - 011 Overlapping Sequence Detector

-

Mealy - 000 آشکارساز توالی همپوشانی Mealy - 000 Overlapping Sequence Detector

-

Mealy - 0101 ردیاب توالی همپوشانی Mealy - 0101 Overlapping Sequence Detector

-

Mealy - 11011 ردیاب توالی همپوشانی Mealy - 11011 Overlapping Sequence Detector

-

طراحی ماشین Mealy - Sequence Detector Designing a Mealy Machine - Sequence Detector

-

مور - 101 آشکارساز توالی غیر همپوشانی Moore - 101 Non-Overlapping Sequence Detector

-

Moore - 010 Non-Overlapping Sequence Detector Moore - 010 Non-Overlapping Sequence Detector

-

Moore - 0101 Non-Overlapping Sequence Detector Moore - 0101 Non-Overlapping Sequence Detector

-

مور - 101 آشکارساز توالی همپوشانی Moore - 101 Overlapping Sequence Detector

-

Moore - 010 ردیاب توالی همپوشانی Moore - 010 Overlapping Sequence Detector

-

Moore - 0101 ردیاب توالی همپوشانی Moore - 0101 Overlapping Sequence Detector

-

طراحی ماشین مور - ردیاب توالی Designing a Moore Machine - Sequence Detector

-

طراحی ماشینی برای انتخاب یک سری توپ رنگی و ماشین فروش Designing a Machine to Pick a Series of Coloured Balls and a Vending Machine

https://donyad.com/d/ea1ebe

Shepherd Tutorials

Shepherd Tutorials

سخت افزار و نرم افزار - طراحی و محصول

نمایش نظرات