آموزش موثر و حرفه ای Verilog با استفاده از FPGA های اینتل و زایلینکس - آخرین آپدیت

دانلود Effective Verilog learning using Intel and Xilinx FPGAs

آموزش جامع توسعه سیستمهای مبتنی بر FPGA اینتل و Xilinx

راهنمای گام به گام برای یادگیری FPGA

این راهنما شما را به صورت گام به گام در توسعه سیستمهای مبتنی بر FPGAهای شرکتهای اینتل و Xilinx راهنمایی میکند.

آنچه در این دوره خواهید آموخت:

- زبان توصیف سختافزار (HDL) - در اینجا از Verilog استفاده میشود.

- ساختارهای مختلف طراحی

- مدیریت کارآمد توسعه

- TCL برای اتوماسیون اعتبارسنجی (Verification-Automation)

هدف اصلی ما FPGAهای شرکت اینتل و ابزارهای توسعهی آن خواهد بود. بخش کوچکی نیز به FPGAهای Xilinx اختصاص داده شده است.

هدف دوره

هدف از این دوره آموزش متخصصان جوان برای توسعهی مستقل سیستمهای دیجیتال است.

محیط توسعه

تمامی مثالها و نرمافزارها در محیط ویندوز (10) اجرا خواهند شد. دانشجویان دارای ویندوز 7 و 8 نیز میتوانند در این دوره شرکت کنند. (متاسفیم برای کاربران لینوکس)

استفاده از برد توسعه اختیاری است. تمامی نرمافزارهای مورد استفاده در این دوره به صورت رایگان در دسترس هستند. اما داشتن یک کامپیوتر با سیستم عامل ویندوز ضروری است.

ما کدهای از پیش توسعه یافته را تجزیه و تحلیل خواهیم کرد تا زمان کافی برای توضیح کدها و قواعد نحوی (syntax) داشته باشیم. این اقدام به منظور کاهش مدت زمان دوره انجام شده است.

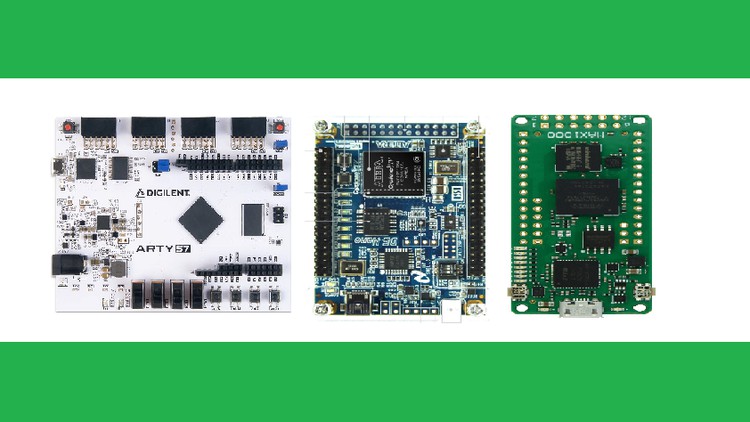

دو برد توسعه مبتنی بر FPGA اینتل و یک برد توسعه مبتنی بر FPGA Xilinx و زنجیره ابزار Xilinx نیز معرفی میشوند.

پیش نیازها

دانشجویانی که با طراحی منطق دیجیتال، الکترونیک دیجیتال یا جبر بولی آشنایی دارند، بهره بیشتری خواهند برد، زیرا این دوره دانش قبلی از منطق دیجیتال و سیستمهای اعداد (دودویی، هگزادسیمال، اکتال، دهدهی) را فرض میکند.

حداقل مقداری دانش در زمینههای مهندسی یا علوم توصیه میشود.

دانشجویانی که با زبانهای C، C++ یا زبانهای مشابه آشنایی دارند، بهره بیشتری خواهند برد.

این دوره به گونهای طراحی شده است که دانشجویان را به توسعهدهندگان مطمئن سیستمهای دیجیتال با استفاده از Verilog و FPGAهای اینتل و AMD تبدیل کند. هر جنبه از زوایای مختلف مورد بحث قرار میگیرد تا کل مفهوم روشنتر شود. این دوره از دو برد توسعه ارزان قیمت FPGA اینتل و یک برد Digilent (AMD) همراه با نرمافزارهای رایگان (Quartus Lite، ModelSim، Vivado) استفاده میکند. خرید بردها کاملاً اختیاری است. این دوره را میتوان بدون بردهای توسعه انجام داد.

علاوه بر این، FPGAها و زنجیرههای ابزار از سایر فروشندگان نیز به طور خلاصه معرفی میشوند.

در این دوره چه چیزی یاد میگیرید؟

- طراحی با استفاده از Verilog HDL (به سادهترین روش ممکن)

- راهاندازی ابزار، که سختترین بخش است.

- اتوماسیون ابزار تکنیکهایی را معرفی میکند که من در طول سالها آموختهام.

- معماریهای مختلف FPGA

- جنبه مدیریتی انتخاب قطعات برای توسعه

- شبیهسازی اطمینان حاصل میکند که آیا طراحی به درستی انجام شده است.

- و بالاتر از همه، من تجربهای را که در طول سالها به دست آوردهام به اشتراک میگذارم.

تذکر مهم: این دوره برای مدت طولانی به روز نشده است. زنجیرههای ابزار Xilinx (اکنون AMD) و Quartus کمی تکامل یافتهاند. لطفاً سعی کنید ابزارها را دانلود کنید و اگر راهاندازی ابزار را متوجه نشدید، در اسرع وقت درخواست بازگشت وجه کنید. من تدریس را به عنوان یک سرگرمی انجام میدهم و تدریس یکی از علایق من است. در صورت تمایل درخواست ارتقاء یا هر گونه کمک را داشته باشید. من اینجا برای شما هستم.

لذت ببرید و در حرفه خود بدرخشید!

Introductions

-

معرفی دوره Introduction to the Course

-

FPGA چیست؟ What is FPGA

-

چگونه یک FPGA انتخاب کنیم؟ How to Choose a FPGA

-

شماره قطعات، شماره پین های FPGAها Part numbers, Pin Numbers of FPGAs

-

انتخاب یک برد توسعه Selecting a Development board

-

جزئیات مربوط به برد MAX1000 Details on MAX1000 baord

-

جزئیات مربوط به برد De0-Nano Details on De0-Nano board

-

پین های ورودی/خروجی (I/O) I/O pins

-

پین های ساعت Clock pins

-

پین های رابط JTAG JTAG Interface pins

-

پین های تغذیه، بانک های پین، توان های درایو Power pins, pin Banks, Drive-Powers

-

آزمون Quiz

نصب نرم افزارها Software Installations

-

نصب Quartus II Prime (Lite/Free) و ModelSim Installing Quartus II Prime (Lite/Free) and ModelSim

-

نصب نرم افزار USB blaster برای DE0-Nano Installing USB blaster software for DE0-Nano

-

نصب نرم افزار USB blaster برای MAX1000 Installing USB blaster software for MAX1000

-

آزمون Quiz

مقدمه ای بر زبان توصیف سخت افزار (HDL) Introduction to Hardware Description Language(HDL)

-

مقدمه ای بر زبان های توصیف سخت افزار (HDLs) Introduction to Hardware Description Languages (HDLs)

-

مبانی Verilog 1 Verilog Fundamentals 1

-

مبانی Verilog 2 Verilog Fundamentals 2

-

مبانی Verilog 3 Verilog Fundamentals 3

-

مبانی Verilog 4 Verilog Fundamentals 4

-

مبانی Verilog 5 Verilog Fundamentals 5

-

مبانی Verilog 6: عملگرها (Operators) Verilog Fundamentals 6 : Operators

-

تئوری فلیپ فلاپ D D Flip-flop theory

-

فلیپ فلاپ D دوست داشتنی ما: ModelSim Our beloved D Flip-flop : ModelSim

-

تئوری Testbench Testbench theory

-

تایید فلیپ فلاپ D در ModelSim: شبیه سازی RTL Verification of D Flip-flop In ModelSim: The RTL Simulation

-

مقدمه ای بر نرم افزار Quartus II Lite Introduction to Quartus II Lite software

-

برنامه ریزی برد Max1000 با فلیپ فلاپ D Programming Max1000 board with D-Flip Flop

-

برنامه ریزی DE0-Nano با فلیپ فلاپ D Programming DE0-Nano with D-Flip Flop

-

گیت ها (Gates) Gates

-

طراحی های چند گیت Multi-gate designs

-

جمع کننده کامل و جمع کننده چند بیتی: Instance ها در Verilog Full Adder and multi-bit adder : The Instances in Verilog

-

شبیه سازی Post Fitting یا Gate level با استفاده از Testbench با استفاده از Quartus-ModelSim Post Fitting or Gate level simulation using Testbench using Quartus-ModelSim

-

آزمون Quiz

ساختارهای طراحی HDL با مثال HDL Design Constructs with Examples

-

HDL: مثال MUX HDL: The MUX Example

-

بلاک MAC (ضرب و تجمع) ساده Simple MAC (Multiplication And Accumulation) block

-

تست MAC MAC testing

-

طراحی شمارنده (Counter) Counter Design

-

تایید شمارنده (Counter) Counter Verification

-

برنامه ریزی شمارنده در DE0 Nano Programming Counter in DE0 Nano

-

برنامه ریزی شمارنده در MAX1000 Programming Counter in MAX1000

-

معرفی ویرایشگر ATOM Introduction to ATOM Editor

-

دو بلوک Always: توضیح سبک کدنویسی Two always blocks : Code Style explained

-

انکودرها (Encoders) Encoders

-

طراحی های پارامتری: طراحی RAM Parameterized Designs: RAM design

-

تست RAM RAM testing

-

ساختارهای Case Case Constructs

-

مثال Case و تایید Case Example and verification

-

Verilog قابل سنتز و غیر قابل سنتز Synthesizable, and non-Synthesizable Verilog

-

آزمون Quiz

زبان TCL و اتوماسیون تست TCL Language and Testing Automation

-

مقدمه TCL TCL Introduction

-

اتوماسیون تایید با استفاده از TCL: روش 1 Verification automation using TCL: Method 1

-

اتوماسیون تایید با استفاده از TCL: روش 2 Verification automation using TCL: Method 2

-

آزمون Quiz

برخی از گزینه های Quartus Some Quartus options

-

مقدمه ای بر Qsys و IP Catalog Introduction to Qsys and IP Catalog

-

استفاده از IP Catalog Using IP Catalog

-

منابع بلوک FPGA و تست هسته های یکپارچه FPGA Block resources and Testing of Integrated cores

-

Quartus Primitives / Standard Verilog Primitives Quartus Primitives / Standard Verilog Primitives

-

مقدمه ای بر فایل های SDC Introduction to SDC files

-

نوشتن و اضافه کردن فایل های SDC به یک پروژه Quartus Writing and Adding SDC files into Quartus a Project

-

آزمون: Quiz :

مباحث پیشرفته و پروژه UART Advance Topics and UART Project

-

مفهوم State Machine State Machine concept

-

Free-Running Finite State Machine (FRFSM) Free-Running Finite State Machine (FRFSM)

-

کدنویسی FRFSM FRFSM : Coding

-

تست Testbench برای FRFSM FRFSM : Testbench testing

-

تست برد FRFSM FRFSM : Board testing

-

Event Driven Finite State Machines Event Driven Finite State Machines

-

Event Driven Finite State Machines: تست با استفاده از برد Event Driven Finite State Machines: Testing using Board

-

Multi Event Driven State machine Multi Event Driven State machine

-

Multi Event Driven State machine: کدنویسی Multi Event Driven State machine : Coding

-

Testbench پویا Dynamic Testbenche

-

تئوری UART: Tx و Rx UART Theory: Tx and Rx

-

کدنویسی UART Tx UART Tx Coding

-

تایید روی برد و کامپیوتر Verification on Board and Computer

-

کدنویسی UART Rx UART Rx Coding

-

تایید روی برد و کامپیوتر Verification on Board and Computer

-

ترکیب Tx و Rx Combining Tx and Rx

-

آزمون: Quiz :

نتیجه گیری: بخش Intel Conclusion: Intel Part

-

مسیر پیش رو Way forward

-

آزمون Quiz

منابع اضافی 1: زنجیره ابزار Xilinx و FPGAها Additional Resources 1: Xilinx Tool chain and FPGAs

-

مقدمه Introduction

-

شماره قطعات و معماری FPGA های سری Xilinx 7 Xilinx 7 series FPGAs part numbers and Architecture

-

برد Xilinx Arty S7-25 از Digilent Xilinx Arty S7-25 board by Digilent

-

نصب Xilinx Vivado Xilinx Vivado Installation

-

شبیه سازی شمارنده در Xilinx Vivado Counter Simulation on Xilinx Vivado

-

مثال شمارنده روی Arty S7-25 Counter example on Arty S7-25

-

انواع توان، بانک های توان Power types, Power banks

-

State Machine روی Arty S7-25 State Machine on Arty S7-25

-

استفاده از SPARTAN 7 Block RAM و تایید Using SPARTAN 7 Block RAM and Verification

-

Verilog Tasks و SystemVerilog Assertions Verilog Tasks and SystemVerilog Assertions

-

Tasks و Assertions؛ کاربردی در Vivado Tasks and Assertions ; Practical in Vivado

-

سیستم های کنترل مبتنی بر رجیستر Register Based Control Systems

-

نتیجه گیری Conclusion

Muhammad Tahir Rana

Muhammad Tahir Rana

نمایش نظرات