آموزش اصول زمانبندی دیجیتال برای مصاحبه VLSI و طراحی SoC - آخرین آپدیت

Digital Timing Basics for VLSI Interview & SoC Design

یک دوره آموزشی VLSI در مورد بررسی های اولیه زمان بندی برای منطق دیجیتال - یک دوره آموزشی ضروری برای دانشجویان و متخصصان VLSI که قصد دارند در طراحی فیزیکی/طراحی جلویی (RTL)/تأیید/طراحی مدار کار کنند.

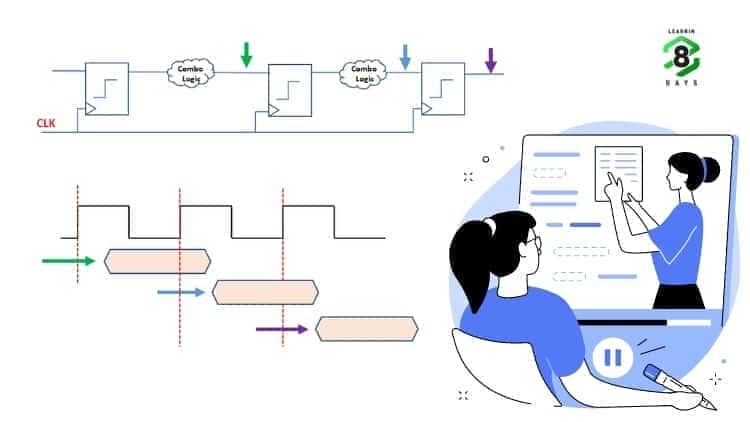

درک زمان بندی Flop، Latch و Logic Gates (زمان تنظیم، زمان نگه داشتن، تاخیر ساعت تا Q) برای هر طراح VLSI بسیار مهم است. چه بهعنوان طراح فیزیکی (بکاند) یا طراح RTL (طراحی جلو) یا مهندس تأیید یا طراح مدار کار میکنید، منطق دیجیتال و زمانبندیهای مرتبط اساس عملکرد طراحی در طراحی SoC را تشکیل میدهند.

کج بودن ساعت یکی دیگر از عوامل مهم در تحلیل زمان بندی استاتیک است. این دوره بیشتر جنبههای زمانبندی فلاپها و نحوه محاسبه حاشیههای تنظیم و نگهداری در طراحی دیجیتال را پوشش میدهد. علاوه بر این، این دوره بینش هایی را در مورد به حداقل رساندن تأخیر، یکی دیگر از جنبه های مهم طراحی فیزیکی، ارائه می دهد.

این یک دوره آموزشی ضروری برای هر مشتاق VLSI است که آرزوی حرفه ای موفق در صنعت نیمه هادی را دارد. اگر برای مصاحبه VLSI یا آزمون GATE آماده می شوید، این دوره برای شما مناسب است.

تمام مفاهیم آموزش داده شده در این مجموعه سخنرانی با مثال های مرتبط دنبال می شود که به دانش آموزان کمک می کند تا درک کاملی از هر مفهوم پیدا کنند. این دوره عالی برای آماده سازی مصاحبه VLSI است.

این دوره آموزشی Crash توسط متخصص صنعت VLSI با ورودیهای متخصصان صنعت که در شرکتهایی مانند Texas Instruments، AMD، Intel، Qualcomm، Rambus، Samsung و غیره کار میکنند، تهیه شده است.

مفاهیم تحت پوشش این دوره عبارتند از - عملیات فلاپ و لچ، زمان تنظیم، زمان نگه داشتن، تاخیر ساعت به Q، بافر، انحراف ساعت، حاشیه تنظیم، حاشیه نگه داشتن، تجزیه و تحلیل مسیر چرخه، پیاده سازی دیجیتال در مقابل فیزیکی، مثالی از تخلفات و رفع آن تخلفات، به حداقل رساندن تأخیر، Clock-Gating و منحنی فرکانس-ولتاژ در SoC.

آرزوها برای سفر VLSI شما!

معرفی Introduction

-

معرفی Introduction

آشنایی با زمان بندی فلاپ Understanding Flop Timings

-

تعاریف پایه Basic Definitions

-

خلاصه سریع Quick Summary

-

زمان راه اندازی و حاشیه راه اندازی Set-up Time & Set-up Margin

-

زمان نگه داشتن و حاشیه نگه دارید Hold time & Hold Margin

-

ساعت به تاخیر Q Clock to Q Delay

بنیاد زمان بندی استاتیک Static Timing Foundation

-

بافر Buffer

-

پیاده سازی منطق Logic Implementation

-

پیاده سازی فیزیکی Physical Implementation

-

شرایط زمانی تنظیم در مسیر چرخه Set-up Time Condition in Cycle Path

-

وضعیت زمان را در مسیر چرخه نگه دارید Hold Time Condition in Cycle Path

-

مثالی برای تنظیم و وضعیت نگهداری Example for Set-up & Hold Condition

حل مسئله برای مصاحبه Problem Solving for Interview

-

تنظیم و نگه داشتن محاسبه حاشیه Set-up & Hold Margin Computation

-

نقض تنظیم Set-up Violation

-

رفع نقض تنظیم: تاخیر مسیر ساعت Set-up Violation Fix : Clock Path Delay

-

نقض نگه دارید Hold Violation

-

رفع نقض نگه داشتن: تاخیر در مسیر داده Hold Violation Fix: Data Path Delay

-

حاشیه خوب اما تاخیر بالاتر Good Margin but Higher Latency

-

کاهش تاخیر با طراحی بهینه Latency Reduction with Optimized Design

-

مسائل طراحی در SoC دنیای واقعی Design Issues in Real World SoC

مفاهیم پیشرفته برای مصاحبه- حاشیه های زمان بندی Advanced Concepts for Interview- Timing Margins

-

چفت مثبت - راه اندازی و زمان نگه داشتن Positive Latch - Setup & Hold Time

-

ضامن منفی - زمان تنظیم و نگهداری Negative Latch - Set-up & Hold Time

-

گیتینگ ساعت - تنظیم و زمان نگه داشتن Clock Gating - Set-up & Hold Time

-

زمان نگه داشتن منفی برای فلاپ Negative Hold Time for Flop

-

زمان تنظیم منفی برای فلاپ Negative Set-up Time for Flop

باورهای غلط رایج Common Misconceptions

-

راه اندازی، نگه داشتن، Clk2Q و Clock Skew Set-up, Hold, Clk2Q and Clock Skew

-

حاشیه را با فرکانس نگه دارید Hold Margin with Frequency

-

تنظیم حاشیه با فرکانس Set-up Margin with Frequency

فرکانس در مقابل ولتاژ در SoC Frequency vs Voltage in SoC

-

منحنی F-V: مقدمه F-V Curve : Introduction

-

منحنی F-V: توضیح F-V Curve: Explanation

طرح عملی شماره 1: مسیرهای موازی چندگانه Practical Design Issue-1: Multiple Parallel Paths

-

چند مسیر - بیان مسئله Multiple Path - Problem Statement

-

چند مسیر - تجزیه و تحلیل زمان راه اندازی Multiple Path - Set-up Time Analysis

-

چند مسیر - تجزیه و تحلیل زمان نگه داشتن Multiple Path - Hold Time Analysis

-

چند مسیر - خلاصه Multiple Path - Summary

موضوع طراحی عملی -2: حداکثر و حداقل فرکانس عملیات Practical Design Issue -2 : Max & Min Frequency of Operation

-

فرکانس عملیات Frequency of Operation

-

حداقل فرکانس عملیات Minimum Frequency of Operation

-

حداکثر فرکانس عملکرد بدون انحراف ساعت Maximum Frequency of Operation without Clock Skew

-

حداکثر فرکانس عملکرد با کج بودن ساعت Maximum Frequency of Operation with Clock Skew

آزمون و مرحله بعدی Quiz & Next Step

-

امتحان Quiz

-

گام بعدی Next Step

https://donyad.com/d/b7ba6a

Learnin28days Academy

Learnin28days Academy

آکادمی آنلاین توسط کارشناسان صنعت برای دانشجویان مهندسی

نمایش نظرات