آموزش متدولوژی تایید جهانی (UVM) + نمایش پروژه - آخرین آپدیت

دانلود Universal Verification Methodology (UVM) + Project Demo

دوره آموزش UVM: توسعه تستبنج، توسعه کیسهای تست، پروژه نمونه و شبیهسازی

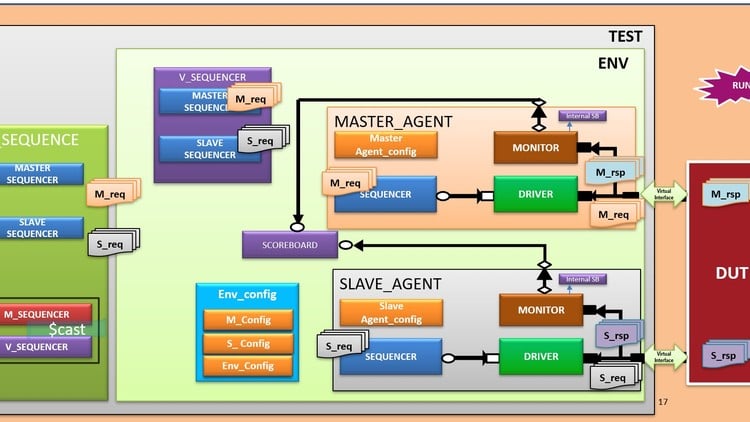

در این دوره جامع، شما با متدولوژی Universal Verification Methodology (UVM) آشنا میشوید و یاد میگیرید چگونه از آن برای ساخت تستبنج برای هر IP دیجیتالی استفاده کنید. این دوره شامل توسعه کیسهای تست با استفاده از SV UVM برای یک IP دیجیتالی، و نحوه شبیهسازی کیسهای تست SV UVM میباشد.

پیشنیازها: اصول اعتبارسنجی (Verification principles)، مبانی دیجیتال (Digital fundamentals)، زبانهای Verilog و SystemVerilog، دستورات لینوکس.

آنچه در این دوره میآموزید:

- مبانی UVM و متدولوژی آن

- اجزا و اشیاء UVM

- UVM Factory

- پیکربندی UVM

- فازهای UVM

- گزارشگیری (Reports) در UVM

- رویکرد گام به گام برای ساخت تستبنج شامل: Driver، Sequencer، Agent، Environment، Test و تستبنج سطح بالا

- ساخت Sequence برای اعتبارسنجی ویژگیهای یک IP نمونه

نتیجه دوره: پس از اتمام این دوره، شما قادر خواهید بود تستبنج UVM و کیسهای تست را از ابتدا توسعه دهید. این دوره همچنین شامل ایجاد یک تستبنج نمونه و توضیح نحوه نوشتن کیسهای تست و شبیهسازی آن میشود. شبیهسازی با استفاده از یک شبیهساز استاندارد انجام میشود.

مناسب برای: این دوره برای دانشجویان رشتههای مهندسی برق، الکترونیک و کامپیوتر (BE/BTech/MTech) که میخواهند UVM را یاد بگیرند و یا قصد انجام کارآموزی دارند، مناسب است. همچنین، فارغالتحصیلان رشتههای مهندسی میتوانند از این دوره برای یادگیری UVM و شبیهسازی با ابزارهای رایگان موجود در edaplayground استفاده کنند.

این دوره یک دوره کامل با نمایش پروژه است و شامل تکالیفی برای تسهیل یادگیری UVM است.

سرفصلهای دوره:

جلسه 01 - مروری بر UVM

جلسه 02 - اجزا و اشیاء UVM

جلسه 03 - TLM

جلسه 04 - UVM Factory

جلسه 05 - پیکربندی UVM

جلسه 06 - فازهای UVM

جلسه 07-1 - گزارشگیری UVM

جلسه 07-2 - مثال گزارشگیری UVM

جلسه 08 - Sequencer و Driver در UVM

جلسه 09 - Agent و Monitor در UVM

جلسه 10 - Test و Scoreboard در UVM

جلسه 11 - توپولوژی UVM

جلسه 12-1 - Sequenceهای تست (بخش 1)

جلسه 12-2 - Sequenceهای تست (بخش 2)

تکالیف

با گذراندن این دوره، میتوانید برای موقعیتهای شغلی در شرکتهای نیمههادی به عنوان مهندس اعتبارسنجی (Design Verification Engineer) درخواست دهید.

مقدمه Introduction

-

مروری بر UVM UVM Overview

-

کامپوننتها و آبجکتهای UVM UVM Components and Objects

-

UVM TLM UVM TLM

-

فکتوری UVM UVM Factory

-

پیکربندی UVM UVM Configuration

-

فازهای UVM UVM Phases

-

گزارشهای UVM UVM reports

-

مثال گزارش UVM UVM Report Example

-

سکانسر و درایور UVM UVM Sequencer and Driver

-

مانیتور و ایجنت UVM UVM Monitor and Agent

-

Scoreboard ،Test ،Sequencer مجازی و Testbench top در UVM UVM Scoreboard, Test, Virtual Sequencer and Testbench top

-

توپولوژی و پرینت در UVM UVM Topology and printing

-

Sequenceهای UVM-01 UVM Sequences-01

-

Sequenceهای UVM-02 UVM Sequences 02

-

تمرینهای آزمایشگاهی UVM UVM Lab exercises

-

تمرین پروژه UVM - اعتبارسنجی حافظه APB UVM Project Assignment - APB memory Verification

-

راه حل برای تمرین پروژه UVM - اعتبارسنجی حافظه APB Solution for UVM Project Assignment - APB Memory Verification

https://donyad.com/d/c19d84

VLSI Mentor

VLSI Mentor

متخصص VLSI، مدیرعامل، فناوریهای VLSI اکسل

![آموزش AZ-104: آمادگی آزمون مدیر Microsoft Azure [2023] آموزش AZ-104: آمادگی آزمون مدیر Microsoft Azure [2023]](https://donyad.com/course/getimg/d133d2b7-6a35-4f00-acc8-ce754b015ef1.jpg)

نمایش نظرات