آموزش UVM برای تأیید قسمت 3: ثبت لایه انتزاعی (RAL) - آخرین آپدیت

UVM for Verification Part 3:Register Abstraction Layer (RAL)

نوشتن میزهای تست Verilog پس از تکمیل طراحی RTL همیشه سرگرم کننده است. می توانید به مشتریان اطمینان دهید که در سناریوهای آزمایش شده طرح بدون اشکال خواهد بود. همانطور که پیچیدگی سیستم روز به روز افزایش می یابد، System Verilog به دلیل قابلیت های قدرتمند و قابلیت استفاده مجدد، به گزینه ای برای تأیید تبدیل می شود که به مهندسان تأیید کمک می کند تا به سرعت باگ های پنهان را پیدا کنند. System Verilog از رویکرد ساختاریافته عقب است، در حالی که UVM برای تشکیل یک اسکلت عمومی سخت کار می کند. افزودن پایگاه داده پیکربندی، روشی را که در گذشته برای کار با زبان تأیید استفاده میکردیم تغییر میدهد. در عرض چند سال، مهندسان تأیید قابلیتهای UVM را شناختند و آن را به عنوان یک استاندارد واقعی برای تأیید طراحی RTL پذیرفتند. UVM یک دوره طولانی در حوزه تأیید خواهد داشت. از این رو، یادگیری در مورد UVM به متقاضیان VLSI کمک می کند تا در این حوزه شغلی را دنبال کنند.

لایه ثبت UVM مجموعه ای از کتابخانه ها را برای استفاده از UVM برای تأیید DUT ها شامل رجیسترها و همچنین حافظه ها ارائه می دهد. UVM RAL مجموعهای از روشهای انتزاعی را برای دسترسی به رجیستر و همچنین حافظهها با مکانیزم دسترسی درب جلو یا پشت در ارائه میکند که به راحتی قابل استفاده و همچنین قابل تنظیم هستند. ما همچنین محاسبات پوششی را که با UVM RAL دریافت می کنیم پوشش خواهیم داد.

افزودن رجیستر و حافظه به محیط تأیید Adding Register and Memory to Verification Environment

-

بررسی اجمالی دوره Course Overview

-

دستور جلسه Agenda

-

مزیت UVM RAL P1 Advantage of UVM RAL P1

-

مزیت UVM RAL P2 Advantage of UVM RAL P2

-

مزیت UVM RAL P3 Advantage of UVM RAL P3

-

مزیت UVM RAL P4 Advantage of UVM RAL P4

-

زمان استفاده از RAL در محیط تأیید When to use RAL in Verification environment

-

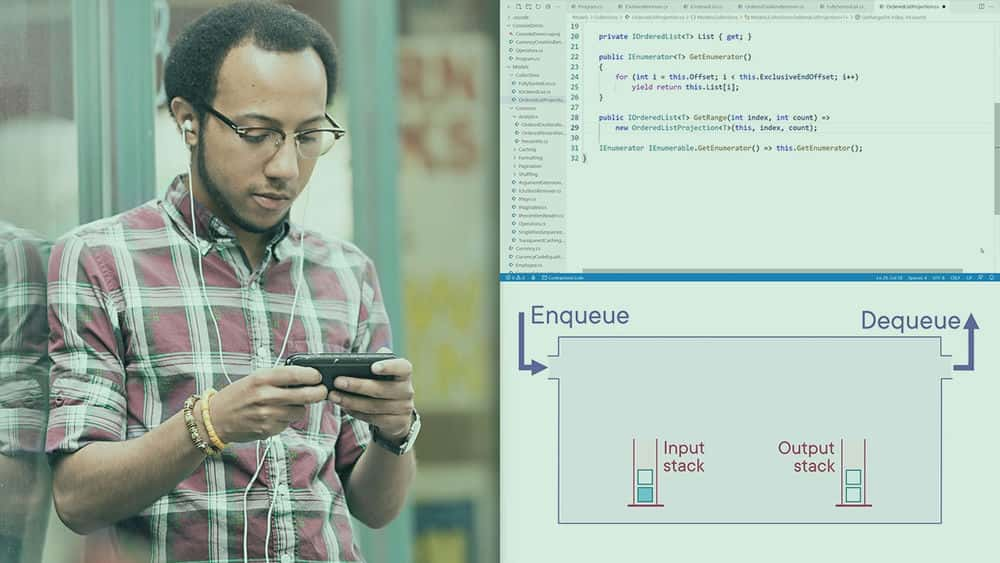

کد Code

-

اجزای رجیستر مدل P1 Components of Register model P1

-

اجزای رجیستر مدل P2 Components of Register model P2

-

اجزای رجیستر مدل P3 Components of Register model P3

-

یادداشت Notes

-

مسیر یادگیری معمولی Typical Learning Path

-

آشنایی با انواع رجیسترها Understanding different types of registers

-

پیاده سازی ثبت در Verification Environmnet P1 Implementation of Register in Verification Environmnet P1

-

پیاده سازی ثبت در Verification Environmnet P2 Implementation of Register in Verification Environmnet P2

-

روشی جایگزین برای افزودن تابع پیکربندی Alternate way of adding configure function

-

خلاصه: پیکربندی تابع Summary : Configure function

-

پیاده سازی ثبت در Verification Environmnet P3 Implementation of Register in Verification Environmnet P3

-

کد Code

-

اسلایدها Slides

-

افزودن ثبت نام با دو فیلد Adding Register with two fields

-

کد Code

-

افزودن ثبت نام با بیت های رزرو شده Adding Register with reserved bits

-

کد Code

-

سیاست دسترسی مختلف P1 Different Access Policy P1

-

سیاست دسترسی متفاوت P2 Different Access Policy P2

-

سیاست دسترسی متفاوت P3 Different Access Policy P3

-

سیاست دسترسی مختلف P4 Different Access Policy P4

-

یادداشت Notes

-

اضافه کردن حافظه P1 Adding Memory P1

-

اضافه کردن حافظه P2 Adding Memory P2

-

کد Code

-

اسلایدها Slides

-

A11 A11

-

A12 A12

افزودن بلاک ثبت نام Adding Register Block

-

دستور جلسه Agenda

-

اضافه کردن Register Block P1 Adding Register Block P1

-

افزودن Register Block P2 Adding Register Block P2

-

افزودن Register Block P3 Adding Register Block P3

-

کد Code

-

اسلایدها Slides

-

A21 A21

آشنایی با آداپتور Understanding Adapter

-

دستور جلسه Agenda

-

استفاده از آداپتور Usage of adapter

-

جریان معمولی Typical flow

-

ساختار ساختار uvm_reg_bus_op Structure of uvm_reg_bus_op struct

-

جریان کامل Complete flow

-

آشنایی با reg2bus Understanding reg2bus

-

آشنایی با bus2reg Understanding bus2reg

-

کد آداپتور با پورت حافظه بومی P1 Adapter code with native memory ports P1

-

کد آداپتور با پورت حافظه بومی P2 Adapter code with native memory ports P2

-

کد آداپتور با پورت های پروتکل خاص P1 Adapter code with Protocol Specific ports P1

-

کد آداپتور با پورت های پروتکل خاص P2 Adapter code with Protocol Specific ports P2

-

خلاصه Summary

-

اسلایدها Slides

-

A31 A31

روش ثبت متفاوت Different Register Method

-

دستور جلسه Agenda

-

انواع پیش بینی کننده: پیش بینی کننده ضمنی Types of Predictor : Implicit Predictor

-

انواع پیش بینی کننده: پیش بینی کننده صریح Types of Predictor : Explicit Predictor

-

انواع پیش بینی کننده: پیش بینی کننده غیرفعال Types of Predictor : Passive Predictor

-

اسلاید Slide

-

ارتباط ترتیبدهنده راننده Driver Sequencer Communication

-

کد Code

-

درک طراحی Understanding Design

-

اضافه کردن Driver + Sequencer Adding Driver + Sequencer

-

افزودن عامل Adding Agent

-

اضافه کردن مدل ثبت نام Adding Register Model

-

اضافه کردن env + uvm test top + testbench top Adding env + uvm test top + testbench top

-

اجرای کد Executing Code

-

کد طراحی Design Code

-

درک ارزشهای مطلوب و منعکس شده Understanding Desired and Mirrored Values

-

روش های مختلف ثبت نام Different register methods

-

کار با ارزش دلخواه Working with Desired Value

-

کد تست Testbench Code

-

کار با Mirrored Value Working with Mirrored Value

-

کد تست Testbench Code

-

درک پیش بینی و آینه Understanding predict and mirror

-

تظاهرات Demonstration

-

کد تست Testbench Code

-

یک معامله خواندن و نوشتن Single Read and Write Transaction

-

چند معامله خواندن و نوشتن Multiple Read and Write Transaction

-

کد تست Testbench Code

-

با استفاده از تصادفی سازی Using randomize

-

کد تست Testbench Code

-

آشنایی با روش های بازنشانی Understanding Reset Methods

-

تظاهرات Demonstration

-

کد تست Testbench Code

-

اتصال روش های بازنشانی به DUT Connecting reset methods to DUT

-

کد تست Testbench Code

-

A41 A41

راه های مختلف دسترسی به Register و Memories Different ways of accessing Register and Memories

-

دستور جلسه Agenda

-

نوع روش های دسترسی p1: Frontdoor Type of access methods p1: Frontdoor

-

نوع روش های دسترسی p2: Backdoor Type of access methods p2: Backdoor

-

نمایش جلو درب Frontdoor Demonstration

-

کد تست Testbench Code

-

اصول دسترسی Backdoor Fundamentals of Backdoor access

-

تظاهرات Demonstration

-

کد طراحی Design Code

-

کد تست Testbench Code

-

Peek و Poke P1 Peek and Poke P1

-

Peek و Poke P2 Peek and Poke P2

-

کد طراحی Design Code

-

کد تست Testbench Code

-

A51 A51

پیش بینی و پوشش صریح Explicit Predictor and Coverage

-

دستور جلسه Agenda

-

درک طراحی برای پیش بینی صریح Understanding Design for Explicit Predictor

-

Building Verification env P1 Building Verification env P1

-

Building Verification env P2 Building Verification env P2

-

Building Verification env P3 Building Verification env P3

-

Building Verification env P4 Building Verification env P4

-

کد تست Testing Code

-

کد طراحی Design Code

-

کد تست Testbench Code

-

تحلیل پوشش P1 Coverage analysis P1

-

تجزیه و تحلیل پوشش P2 Coverage analysis P2

-

تحلیل پوشش P3 Coverage analysis P3

-

کد طراحی Design Code

-

کد تست Testbench Code

-

اجرا کن run.do

کار با حافظه ها Working with Memories

-

دستور جلسه Agenda

-

درک طراحی Understanding Design

-

ساختمان DRV + MON + SCO + AGENT Building DRV + MON + SCO + AGENT

-

مدل ثبت ساختمان Building Register model

-

افزودن توالی ثبت: تراکنش واحد Adding Register sequence : Single Transaction

-

اضافه کردن توالی ثبت: تراکنش های متعدد Adding Register sequence : Multiple Transactions

-

کد طراحی Design Code

-

کد تست Testbench Code

-

معاملات پشت سر هم Burst Transactions

-

کد طراحی Design Code

-

کد تست Testbench Code

-

محاسبه پوشش برای حافظه P1 Coverage computation for memory P1

-

محاسبه پوشش برای حافظه P2 Coverage computation for memory P2

-

کد طراحی Design Code

-

کد تست Testbench Code

پروژه کامل Complete Project

-

دستور جلسه Agenda

-

درک طراحی P1 Understanding Design P1

-

طراحی P2 را درک کنید Understand Design P2

-

محیط تأیید ساختمان P1 Building Verification environment P1

-

محیط تأیید ساختمان P2 Building Verification environment P2

-

ثبت ساختمان مدل P1 Building Register model P1

-

ثبت ساختمان مدل P2 Building Register model P2

-

اضافه کردن صفحه تست Adding testbench top

-

تست DUT Testing DUT

-

کد طراحی Design Code

-

کد تست Testbench Code

-

A81 A81

-

A82 A82

https://donyad.com/d/8a2fa5

Kumar Khandagle

Kumar Khandagle

رهبر توسعه دهنده FPGA @ FinTech

نمایش نظرات