آموزش پروتکل PCIe Gen 6.0: اصول اولیه تا پیشرفته (VLSI) - آخرین آپدیت

دانلود PCIe Gen 6.0 Protocol : Basics to Advanced (VLSI)

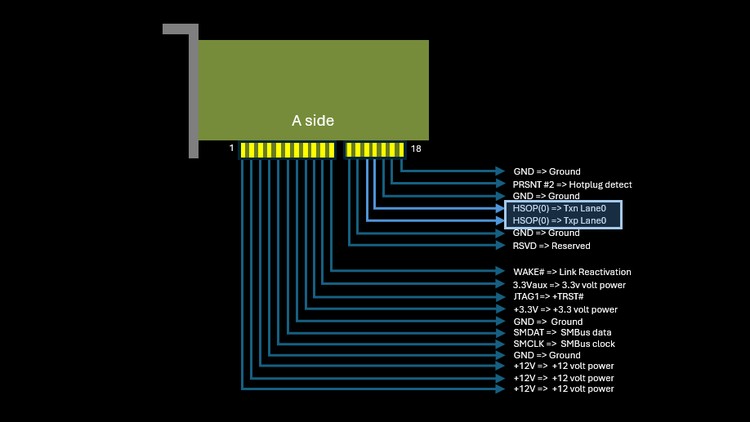

پتانسیل فناوری PCIe Gen 6 را با این دوره تخصصی که برای مهندسین طراحی و تأیید ASIC طراحی شده است، باز کنید. PCIe (Peripheral Component Interconnect Express) به سنگ بنای سیستم های اتصال پرسرعت مدرن تبدیل شده است و Gen 6 پیشرفت های پیشگامانه ای را برای پاسخگویی به نیازهای نسل بعدی محاسبات، شبکه و برنامه های ذخیره سازی معرفی می کند. این دوره یک درک جامع از لایه تراکنش PCIe Gen 6 ارائه می دهد که بر مدیریت فضای آدرس، مسیریابی تراکنش ها و پیشرفت های معماری که آن را از نسل های قبلی متمایز می کند تمرکز دارد.

از طریق ماژولهای ساختیافته، مفاهیم اساسی، از جمله قالبهای بسته، مکانیسمهای کنترل جریان، و معرفی رمزگذاری FLIT (واحد کنترل جریان) را کشف خواهید کرد - یک ویژگی حیاتی که قابلیتهای پهنای باند چشمگیر Gen 6 را قادر میسازد. این دوره به بررسی سازگاری قبلی PCIe Gen 6 با نسخه های قبلی می پردازد و از ادغام یکپارچه با سیستم های موجود اطمینان می دهد. شما اطلاعاتی در مورد اینکه چگونه Gen 6 به پهنای باند دو برابر نسل 5 دست می یابد و در عین حال به کارایی انرژی و مقیاس پذیری سیستم می پردازد، به دست خواهید آورد.

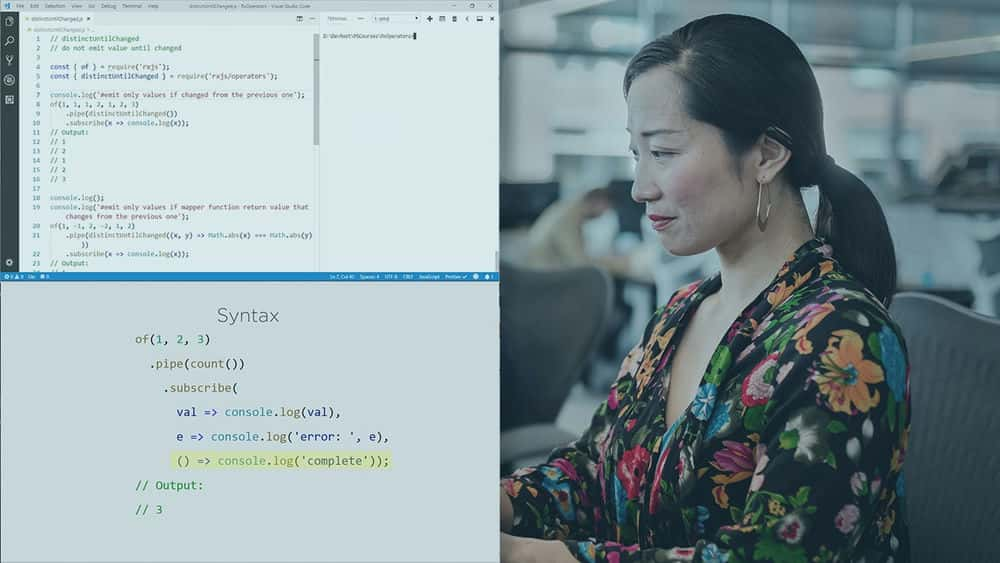

شرکتکنندگان همچنین به موضوعات پیشرفتهای مانند چالشهای سیگنالدهی با سرعت بالا، رمزگذاری PAM4 (مدولاسیون دامنه پالس)، الزامات کلاکینگ، و مکانیسمهای رسیدگی به خطا منحصر به فرد نسل 6 میپردازند. تاکید بر ملاحظات طراحی عملی و استراتژیهای راستیآزمایی قوی است استفاده از روشهای استاندارد صنعتی مانند UVM (روش تأیید جهانی). مثالهای عملی، سناریوهای آزمایشی، و مطالعات موردی در دنیای واقعی، درک عمیقی از پیادهسازی و آزمایش انطباق ارائه میدهند.

این دوره برای تجهیز مهندسان به تخصص طراحی و تأیید سیستم های PCIe Gen 6 با اطمینان طراحی شده است. چه در حال کار بر روی طراحی های پیشرفته ASIC باشید و چه از انطباق با استانداردهای دقیق تأیید اطمینان حاصل کنید، این دوره شما را قادر می سازد تا به طور موثر با چالش های پیچیده مقابله کنید. با تسلط بر PCIe Gen 6 - ستون فقرات محاسباتی با کارایی بالا و برنامه های کاربردی داده فشرده، در صنعت نیمه هادی ها پیشرو باشید. به ما بپیوندید و مهارت های خود را به سطح بعدی ارتقا دهید.

مقدمه و بررسی اجمالی Introduction and Overview

-

درباره مربی About Instructor

-

معرفی پروتکل PCIe PCIe Protocol Introduction

-

مروری بر معماری PCIe PCIe Architecture Overview

-

بررسی اجمالی لایه تراکنش Transaction Layer Overview

-

کیفیت خدمات (QoS) و کنترل جریان Quality of Service (QoS ) and Flow Control

-

مروری بر PCIe 6.0 PCIe 6.0 Overview

-

نمای کلی لایه پیوند داده Data Link Layer Overview

-

نمای کلی لایه فیزیکی Physical Layer Overview

نمای کلی پیکربندی، شمارش و مسیریابی Configuration Overview, Enumeration and Routing

-

نمای کلی پیکربندی Configuration Overview

-

مکانیسم پیکربندی Configuration Mechanism

-

شمارش Enumeration

-

فضای آدرس و مسیریابی تراکنش Address space and Transaction routing

Transaction Layer Gen 5.0 Transaction Layer Gen 5.0

-

ساختار PCIe Gen 5.0 TLP PCIe Gen 5.0 TLP Structure

-

درخواست حافظه TLP Memory Request TLP

-

تکمیل TLP Completion TLP

-

پیکربندی TLP Configuration TLP

-

IO درخواست TLP IO Request TLP

-

TLP پیام دهید Message TLP

-

فلو کوترول Flow Cotrol

-

سفارش تراکنش Transaction Ordering

Transaction Layer Gen 6.0 Transaction Layer Gen 6.0

-

PCIE Gen 6.0 Flit Format PCIE Gen 6.0 Flit Format

-

تفاوت فرمت Gen 5.0 با Gen 6.0 Format Differences of Gen 5.0 vs Gen 6.0

-

PCIE Gen 6.0 Flit Packing/Unpacking PCIE Gen 6.0 Flit Packing/Unpacking

Data Link Layer Gen 5.0 Data Link Layer Gen 5.0

-

عملکرد Gen 5.0/NFM (حالت غیر فلش). Gen 5.0/ NFM (Non Flit Mode) Operation

Data Link Layer Gen 6.0 Data Link Layer Gen 6.0

-

عملیات لایه پیوند داده Gen 6.0/FM (حالت Flit). Gen 6.0/FM (Flit Mode) Data Link Layer Operation

-

مکانیسم استاندارد ACK/NAK Gen 6.0 Gen 6.0 Standard ACK/NAK Mechanism

-

مکانیزم انتخابی ACK/NAK Grn 6.0 Grn 6.0 Selective ACK/NAK Mechanism

لایه فیزیکی Physical Layer

-

نمای کلی لایه فیزیکی Gen 5.0 Gen 5.0 Physical Layer Overview

-

رابط PIPE لایه فیزیکی Physical Layer PIPE Interface

-

رمزگذاری/درک نمودار چشمی Encoding/Eye Diagram Understanding

-

جزئیات آنالوگ Front End و برابرسازی Analog Front End details and eqaulization

-

کلاکینگ معماری/یکپارچگی سیگنال Clocking Architecture/Signal Integrity

-

انواع مجموعه سفارشی Ordered Set types

-

راه اندازی پیوند و آموزش (LTSSM) Link Initialization and Training (LTSSM)

-

راه اندازی پیوند و آموزش (LTSSM) Link Initialization and Training (LTSSM)

-

نمای کلی LTSSM Full LTSSM Overview

-

Gen 6.0 Link Training Gen 6.0 Link Training

-

روش های اشکال زدایی LTSSM LTSSM Debug methods

-

تحولات Gen 7.0 Gen 7.0 Developments

-

مواد منبع و اسناد تکمیلی Resource Materials and Supplemental Documents

https://donyad.com/d/91353e

Asiclab VLSI Academy

Asiclab VLSI Academy

مربی در Udemy

نمایش نظرات